- 您现在的位置:买卖IC网 > PDF目录16836 > AD9549A/PCBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9549A PDF资料下载

参数资料

| 型号: | AD9549A/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 67/76页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9549A |

| 设计资源: | AD9549 Schematics AD9549 Gerber Files |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9549A |

| 主要属性: | 8 kHz ~ 750 MHz 输入 |

| 次要属性: | 差分输出 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 7 of 76

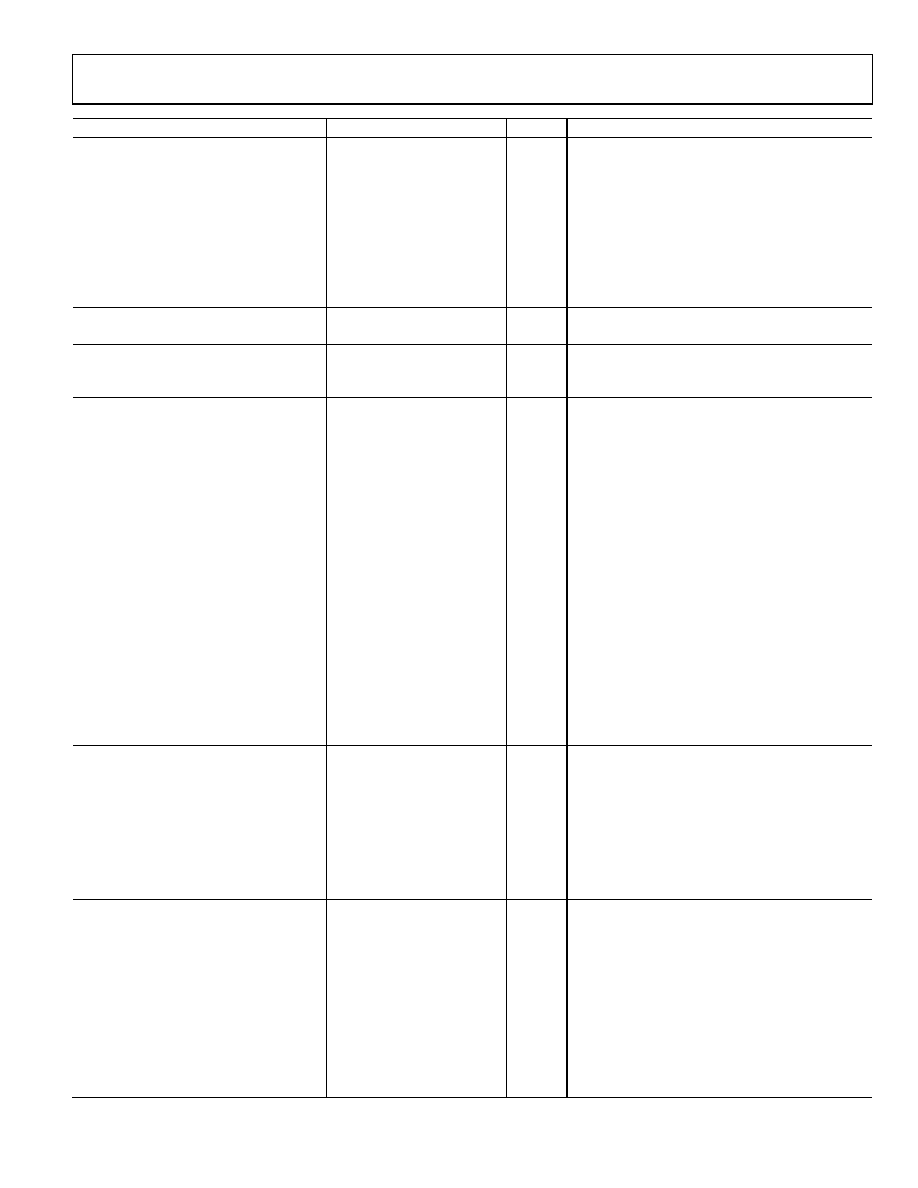

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CMOS Output Driver

(AVDD3/Pin 37) @ 3.3 V

Frequency Range

0.008

150

MHz

See

Figure 14 for maximum toggle rate

Duty Cycle

45

55

65

%

With 20 pF load and up to 150 MHz

Rise Time/Fall Time (20-80%)

3

4.6

ns

With 20 pF load

CMOS Output Driver

(AVDD3/Pin 37) @ 1.8 V

Frequency Range

0.008

40

MHz

See

Figure 13 for maximum toggle rate

Duty Cycle

45

55

65

%

With 20 pF load and up to 40 MHz

Rise Time/Fall Time (20% to 80%)

5

6.8

ns

With 20 pF load

HOLDOVER

Frequency Accuracy

See the

Holdover section

OUTPUT FREQUENCY SLEW LIMITER

Slew Rate Resolution

0.54

111

Hz/sec

P = 216 for minimum; P = 25 for maximum

Slew Rate Range

0

3 × 1016

Hz/sec

P = 216 for minimum; P = 25 for maximum

REFERENCE MONITORS

Loss of Reference Monitor

Operating Frequency Range

7.63 × 103

167 × 106

Hz

Minimum Frequency Error for

Continuous REF Present Indication

16

ppm

fREF = 8 kHz

Minimum Frequency Error for

Continuous REF Present Indication

19

%

fREF = 155 MHz

Maximum Frequency Error for

Continuous REF Lost Indication

32

ppm

fREF = 8 kHz

Maximum Frequency Error for

Continuous REF Lost Indication

35

%

fREF = 155 MHz

Reference Quality Monitor

Operating Frequency Range

0.008

150

MHz

Frequency Resolution (Normalized)

0.2

ppm

fREF = 8 kHz; OOL divider = 65,535 for minimum; OOL

divider = 1 for max (see the

Monitor section)

Frequency Resolution (Normalized)

408

ppm

fREF = 155 MHz; OOL divider = 65,535 for minimum;

OOL divider = 1 for maximum

Validation Timer

See the

Timing Range

32 × 109

137

sec

PIO = 5

Timing Range

65 × 106

2.8 × 105

sec

PIO = 16

DAC OUTPUT CHARACTERISTICS

DCO Frequency Range (1st Nyquist Zone)

10

450

MHz

DPLL loop bandwidth sets lower limit

Output Resistance

50

Single-ended (each pin internally terminated to AVSS)

Output Capacitance

5

pF

Full-Scale Output Current

20

31.7

mA

Range depends on DAC RSET resistor

Gain Error

10

+10

% FS

Output Offset

0.6

μA

Voltage Compliance Range

AVSS

0.50

+0.5

AVSS +

0.50

Outputs not dc-shorted to VSS

DIGITAL PLL

Minimum Open-Loop Bandwidth

0.1

Hz

Dependent on the frequency of REFA/REFB, the DAC

sample rate, and the P-, R-, and S-divider values

Maximum Open-Loop Bandwidth

100

kHz

Dependent on the frequency of REFA/REFB, the DAC

sample rate, and the P-, R-, and S-divider values

Minimum Phase Margin

0

10

Degrees

Dependent on the frequency of REFA/REFB, the DAC

sample rate, and the P-, R-, and S-divider values

Maximum Phase Margin

85

90

Degrees

Dependent on the frequency of REFA/REFB, the DAC

sample rate, and the P-, R-, and S-divider values

PFD Input Frequency Range

~0.008

~24.5

MHz

Feedforward Divider Ratio

1

131,070

1, 2, …, 65,535 or 2, 4, …, 131,070

Feedback Divider Ratio

1

131,070

1, 2, …, 65,535 or 2, 4, …, 131,070

相关PDF资料 |

PDF描述 |

|---|---|

| ESC05DRTS-S734 | CONN EDGECARD 10POS DIP .100 SLD |

| MAX6250BEPA+ | IC VREF SERIES BURIED ZNR 8-PDIP |

| MAX6133A30+T | IC VREF SERIES PREC 3V 8-UMAX |

| MAX6133A41+T | IC VREF SERIES PREC 4.096V 8UMAX |

| MAX6133A50+T | IC VREF SERIES PREC 5V 8-UMAX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9550 | 制造商:AD 制造商全称:Analog Devices 功能描述:Integer-N Clock Translator for Wireline Communications |

发布紧急采购,3分钟左右您将得到回复。