- 您现在的位置:买卖IC网 > PDF目录1900 > ADUC7021BCPZ62-RL7 (Analog Devices Inc)IC MCU 12BIT 1MSPS UART 40-LFCSP PDF资料下载

参数资料

| 型号: | ADUC7021BCPZ62-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 41/92页 |

| 文件大小: | 0K |

| 描述: | IC MCU 12BIT 1MSPS UART 40-LFCSP |

| 标准包装: | 750 |

| 系列: | MicroConverter® ADuC7xxx |

| 核心处理器: | ARM7 |

| 芯体尺寸: | 16/32-位 |

| 速度: | 44MHz |

| 连通性: | EBI/EMI,I²C,SPI,UART/USART |

| 外围设备: | PLA,PWM,PSM,温度传感器,WDT |

| 输入/输出数: | 13 |

| 程序存储器容量: | 64KB(32K x 16) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 2K x 32 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 3.6 V |

| 数据转换器: | A/D 8x12b,D/A 2x12b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7019/20/21/22/24/25/26/27/28

Rev. B | Page 46 of 92

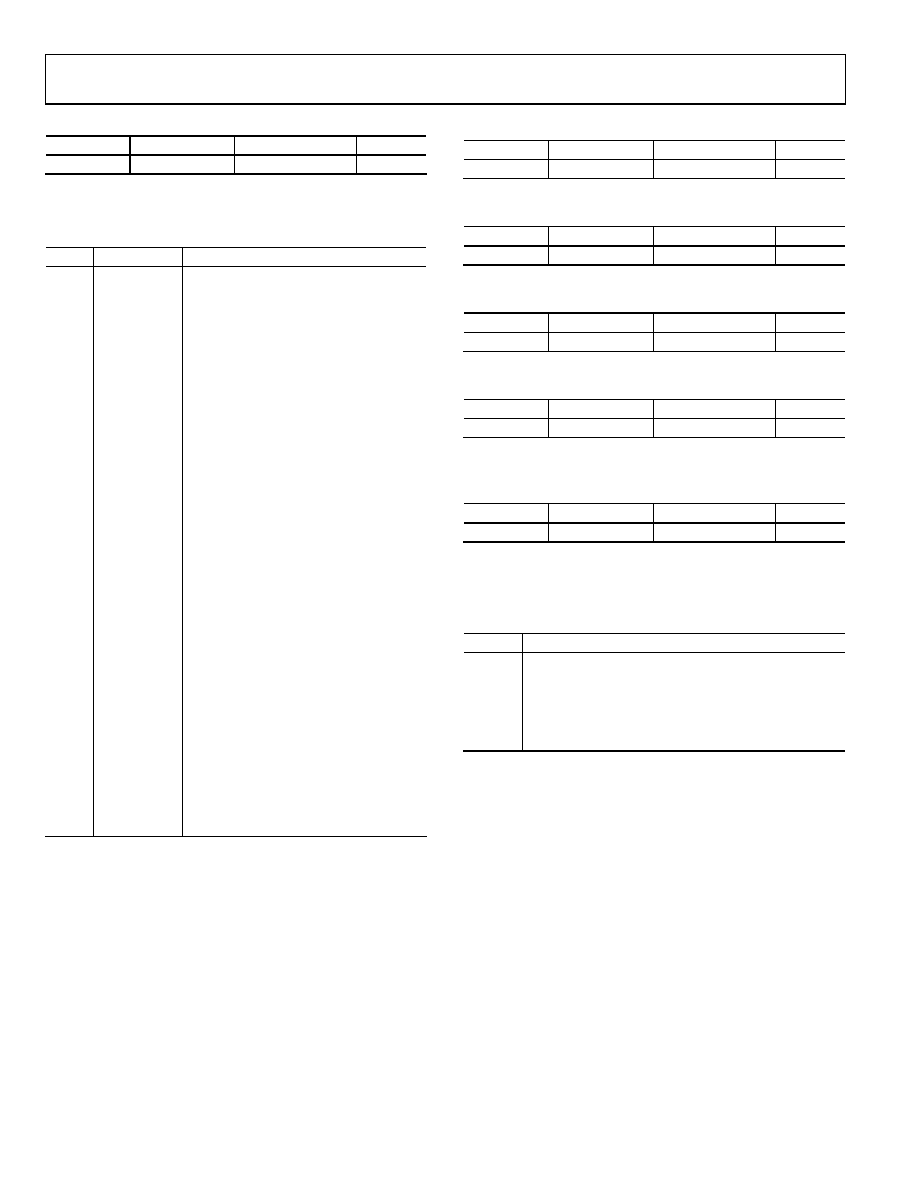

FEECON Register

Name

Address

Default Value

Access

FEECON

0xFFFFF808

0x07

R/W

FEECON is an 8-bit command register. The commands are

described in Table 22.

Table 22. Command Codes in FEECON

Code

Command

Description

Null

Idle State.

Single Read

Load FEEDAT with the 16-bit data.

Indexed by FEEADR.

Single Write

Write FEEDAT at the address pointed by

FEEADR. This operation takes 50

μs.

Erase/Write

Erase the page indexed by FEEADR and

write FEEDAT at the location pointed by

FEEADR. This operation takes

approximately 24 ms.

Single Verify

Compare the contents of the location

pointed by FEEADR to the data in

FEEDAT. The result of the comparison is

returned in FEESTA Bit 1.

Single Erase

Erase the page indexed by FEEADR.

Mass Erase

Erase 62 kB of user space. The 2 kB of

kernel are protected. This operation

takes 2.48 sec. To prevent accidental

execution, a command sequence is

required to execute this instruction.

See the Command Sequence for

Executing a Mass Erase section.

0x07

Reserved

Reserved.

0x08

Reserved

Reserved.

0x09

Reserved

Reserved.

0x0A

Reserved

Reserved.

0x0B

Signature

Give a signature of the 64 kB of Flash/EE

in the 24-bit FEESIGN MMR. This

operation takes 32,778 clock cycles.

0x0C

Protect

This command can run only once. The

value of FEEPRO is saved and removed

only with a mass erase (0x06) or the key.

0x0D

Reserved

Reserved.

0x0E

Reserved

Reserved.

0x0F

Ping

No operation; interrupt generated.

1 The FEECON register always reads 0x07 immediately after execution of any

of these commands.

FEEDAT Register

Name

Address

Default Value

Access

FEEDAT

0xFFFFF80C

0xXXXX

R/W

FEEDAT is a 16-bit data register.

FEEADR Register

Name

Address

Default Value

Access

FEEADR

0xFFFFF810

0x0000

R/W

FEEADR is another 16-bit address register.

FEESIGN Register

Name

Address

Default Value

Access

FEESIGN

0xFFFFF818

0xFFFFFF

R

FEESIGN is a 24-bit code signature.

FEEPRO Register

Name

Address

Default Value

Access

FEEPRO

0xFFFFF81C

0x00000000

R/W

FEEPRO MMR provides protection following a subsequent

reset of the MMR. It requires a software key (see Table 23).

FEEHIDE Register

Name

Address

Default Value

Access

FEEHIDE

0xFFFFF820

0xFFFFFFFF

R/W

FEEHIDE MMR provides immediate protection. It does not

require any software key. Note that the protection settings in

FEEHIDE are cleared by a reset. (see Table 23).

Table 23. FEEPRO and FEEHIDE MMR Bit Designations

Bit

Description

31

Read Protection. Cleared by user to protect all code.

Set by user to allow reading the code.

30:0

Write Protection for Page 123 to Page 120, Page 119

to Page 116, and Page 0 to Page 3. Cleared by user to

protect the pages in writing. Set by user to allow

writing the pages.

Command Sequence for Executing a Mass Erase

FEEDAT=0x3CFF;

FEEADR = 0xFFC3;

FEEMOD= FEEMOD|0x8;

//Erase key enable

FEECON=0x06;

//Mass erase command

相关PDF资料 |

PDF描述 |

|---|---|

| ADUC7023BCPZ62I-R7 | IC MCU 12BIT 62KB FLASH 32LFCSP |

| ADUC7024BCPZ62 | IC MCU FLSH 62K ANLG I/O 64LFCSP |

| ADUC7032BSTZ-88 | IC MCU 96K FLASH DUAL 48LQFP |

| ADUC7032BSTZ-8V-RL | IC BATTERY SENSOR PREC 48-LQFP |

| ADUC7034BCPZ | IC MCU FLASH 32K ANLG IO 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADUC7022 | 制造商:AD 制造商全称:Analog Devices 功能描述:Precision Analog Microcontroller 12-bit Analog I/O, ARM7TDMI MCU |

| ADUC7022ACP32 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

| ADUC7022ACPZ32 | 制造商:Analog Devices 功能描述:MCU 32BIT RISC 32KB FLASH 3.3V 40LFCSP EP - Trays |

| ADUC7022BCP32 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

| ADUC7022BCP62 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

发布紧急采购,3分钟左右您将得到回复。