- 您现在的位置:买卖IC网 > PDF目录1900 > ADUC7021BCPZ62-RL7 (Analog Devices Inc)IC MCU 12BIT 1MSPS UART 40-LFCSP PDF资料下载

参数资料

| 型号: | ADUC7021BCPZ62-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 68/92页 |

| 文件大小: | 0K |

| 描述: | IC MCU 12BIT 1MSPS UART 40-LFCSP |

| 标准包装: | 750 |

| 系列: | MicroConverter® ADuC7xxx |

| 核心处理器: | ARM7 |

| 芯体尺寸: | 16/32-位 |

| 速度: | 44MHz |

| 连通性: | EBI/EMI,I²C,SPI,UART/USART |

| 外围设备: | PLA,PWM,PSM,温度传感器,WDT |

| 输入/输出数: | 13 |

| 程序存储器容量: | 64KB(32K x 16) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 2K x 32 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 3.6 V |

| 数据转换器: | A/D 8x12b,D/A 2x12b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7019/20/21/22/24/25/26/27/28

Rev. B | Page 70 of 92

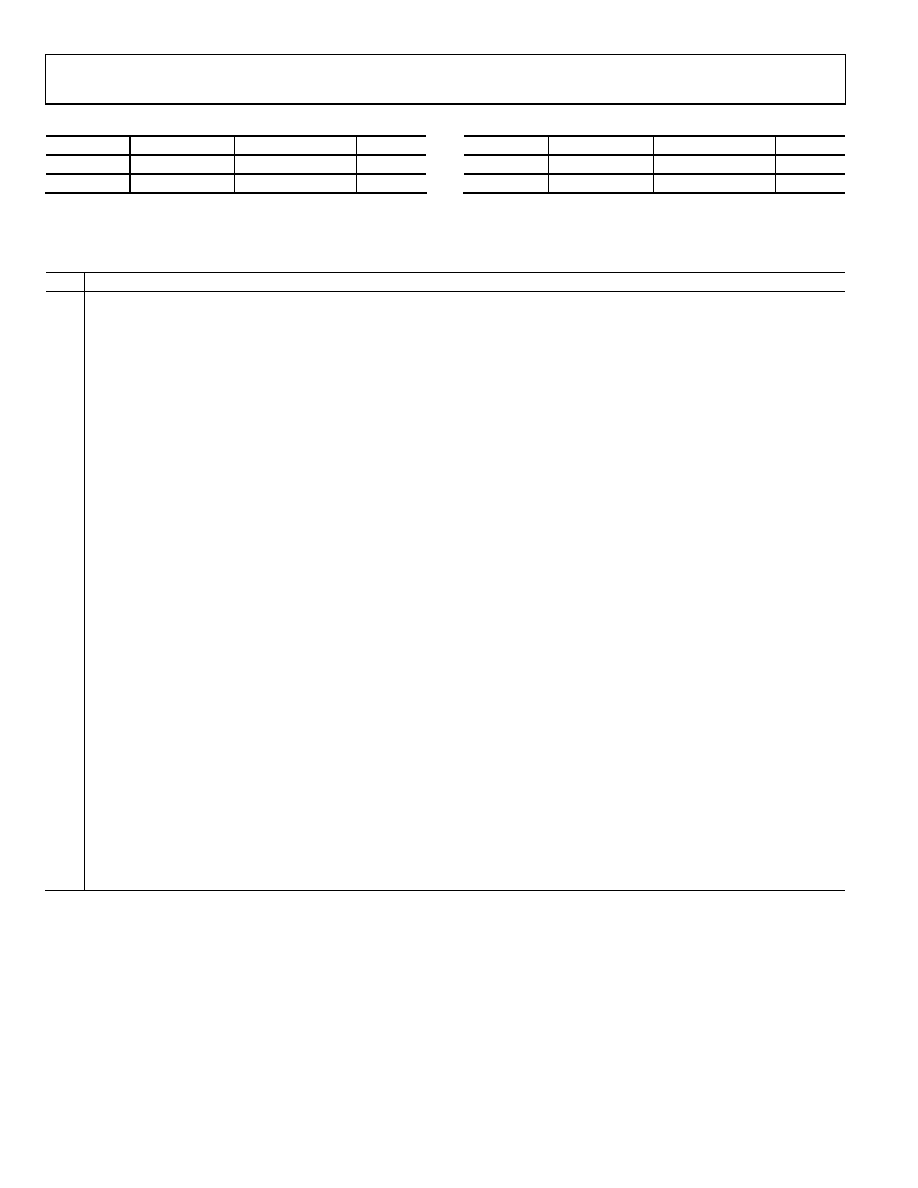

I2CxALT Registers

Name

Address

Default Value

Access

I2C0ALT

0xFFFF0828

0x00

R/W

I2C1ALT

0xFFFF0928

0x00

R/W

I2CxALT are hardware general call ID registers used in slave mode.

I2CxCFG Registers

Name

Address

Default Value

Access

I2C0CFG

0xFFFF082C

0x00

R/W

I2C1CFG

0xFFFF092C

0x00

R/W

I2CxCFG are configuration registers.

Table 63. I2C0CFG MMR Bit Descriptions

Bit

Description

31:5

Reserved. These bits should be written by the user as 0.

14

Enable Stop Interrupt. Set by the user to generate an interrupt upon receiving a stop condition and after receiving a valid start

condition and matching address. Cleared by the user to disable the generation of an interrupt upon receiving a stop condition.

13

Reserved.

12

Reserved.

11

Enable Stretch SCL (Holds SCL low). Set by the user to stretch the SCL line. Cleared by the user to disable stretching of the SCL line.

10

Reserved.

9

Slave Tx FIFO Request Interrupt Enable. Set by the user to disable the slave Tx FIFO request interrupt. Cleared by the user to generate

an interrupt request just after the negative edge of the clock for the R/W bit. This allows the user to input data into the slave Tx FIFO if

it is empty. At 400 ksps and the core clock running at 41.78 MHz, the user has 45 clock cycles to take appropriate action, taking

interrupt latency into account.

8

General Call Status Bit Clear. Set by the user to clear the general call status bits. Cleared automatically by hardware after the general

call status bits have been cleared.

7

Master Serial Clock Enable Bit. Set by user to enable generation of the serial clock in master mode. Cleared by user to disable serial

clock in master mode.

6

Loop Back Enable Bit. Set by user to internally connect the transition to the reception to test user software. Cleared by user to operate

in normal mode.

5

Start Back-Off Disable Bit. Set by user in multimaster mode. If losing arbitration, the master immediately tries to retransmit. Cleared by

user to enable start back-off. After losing arbitration, the master waits before trying to retransmit.

4

Hardware General Call Enable. When this bit and Bit 3 are set, and have received a general call (Address 0x00) and a data byte, the

device checks the contents of the I2C0ALT against the receive register. If the contents match, the device has received a hardware

general call. This is used if a device needs urgent attention from a master device without knowing which master it needs to turn to.

This is a “to whom it may concern” call. The ADuC7019/20/21/22/24/25/26/27/28 watch for these addresses. The device that requires

attention embeds its own address into the message. All masters listen and the one that can handle the device contacts its slave and

acts appropriately. The LSB of the I2C0ALT register should always be written to 1, as per the I2C January 2000 bus specification.

3

General Call Enable Bit. Set this bit to enable the slave device to ACK an I2C general call, Address 0x00 (write). The device then

recognizes a data bit. If it receives a 0x06 (reset and write programmable part of slave address by hardware) as the data byte, the I2C

interface resets as per the I2C January 2000 bus specification. This command can be used to reset an entire I2C system. The general

call interrupt status bit sets on any general call. The user must take corrective action by setting up the I2C interface after a reset. If it

receives a 0x04 (write programmable part of slave address by hardware) as the data byte, the general call interrupt status bit sets on

any general call. The user must take corrective action by reprogramming the device address.

2

Reserved.

1

Master Enable Bit. Set by user to enable the master I2C channel. Cleared by user to disable the master I2C channel.

0

Slave Enable Bit. Set by user to enable the slave I2C channel. A slave transfer sequence is monitored for the device address in I2C0ID0,

I2C0ID1, I2C0ID2, and I2C0ID3. If the device address is recognized, the part participates in the slave transfer sequence. Cleared by user

to disable the slave I2C channel.

相关PDF资料 |

PDF描述 |

|---|---|

| ADUC7023BCPZ62I-R7 | IC MCU 12BIT 62KB FLASH 32LFCSP |

| ADUC7024BCPZ62 | IC MCU FLSH 62K ANLG I/O 64LFCSP |

| ADUC7032BSTZ-88 | IC MCU 96K FLASH DUAL 48LQFP |

| ADUC7032BSTZ-8V-RL | IC BATTERY SENSOR PREC 48-LQFP |

| ADUC7034BCPZ | IC MCU FLASH 32K ANLG IO 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADUC7022 | 制造商:AD 制造商全称:Analog Devices 功能描述:Precision Analog Microcontroller 12-bit Analog I/O, ARM7TDMI MCU |

| ADUC7022ACP32 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

| ADUC7022ACPZ32 | 制造商:Analog Devices 功能描述:MCU 32BIT RISC 32KB FLASH 3.3V 40LFCSP EP - Trays |

| ADUC7022BCP32 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

| ADUC7022BCP62 | 制造商:Analog Devices 功能描述:FLASH ARM7+10-CH,12-B ADC IC - Trays |

发布紧急采购,3分钟左右您将得到回复。