- 您现在的位置:买卖IC网 > PDF目录224103 > K4T56163QI-ZLD50 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 PDF资料下载

参数资料

| 型号: | K4T56163QI-ZLD50 |

| 元件分类: | DRAM |

| 英文描述: | 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 |

| 封装: | ROHS COMPLIANT, FBGA-84 |

| 文件页数: | 36/42页 |

| 文件大小: | 727K |

| 代理商: | K4T56163QI-ZLD50 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页

Rev. 1.0 October 2007

DDR2 SDRAM

K4T56163QI

41 of 42

36. These parameters are specified per their average values, however it is understood that the following relationship between the average timing and the

absolute instantaneous timing holds at all times. (Min and max of SPEC values are to be used for calculations in the table below.)

Example: For DDR2-667, tCH(abs),min = ( 0.48 x 3000 ps ) - 125 ps = 1315 ps

37. tHP is the minimum of the absolute half period of the actual input clock. tHP is an input parameter but not an input specification parameter. It is used

in conjunction with tQHS to derive the DRAM output timing tQH. The value to be used for tQH calculation is determined by the following equation;

tHP = Min ( tCH(abs), tCL(abs) ),

where,

tCH(abs) is the minimum of the actual instantaneous clock HIGH time;

tCL(abs) is the minimum of the actual instantaneous clock LOW time;

38. tQHS accounts for:

1) The pulse duration distortion of on-chip clock circuits, which represents how well the actual tHP at the input is transferred to the output; and

2) The worst case push-out of DQS on one transition followed by the worst case pull-in of DQ on the next transition, both of which are independent of

each other, due to data pin skew, output pattern effects, and p-channel to n-channel variation of the output drivers

39. tQH = tHP - tQHS, where:

tHP is the minimum of the absolute half period of the actual input clock; and tQHS is the specification value under the max column.

{The less half-pulse width distortion present, the larger the tQH value is; and the larger the valid data eye will be.}

Examples:

1) If the system provides tHP of 1315 ps into a DDR2-667 SDRAM, the DRAM provides tQH of 975 ps minimum.

2) If the system provides tHP of 1420 ps into a DDR2-667 SDRAM, the DRAM provides tQH of 1080 ps minimum.

40. When the device is operated with input clock jitter, this parameter needs to be derated by the actual tERR(6-10per) of the input clock. (output derat-

ings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-667 SDRAM has tERR(6-10per),min = - 272 ps and tERR(6-10per),max = + 293 ps, then

tDQSCK,min(derated) = tDQSCK,min - tERR(6-10per),max = - 400 ps - 293 ps = - 693 ps and tDQSCK,max(derated) = tDQSCK,max - tERR(6-

10per),min = 400 ps + 272 ps = + 672 ps. Similarly, tLZ(DQ) for DDR2-667 derates to tLZ(DQ),min(derated) = - 900 ps - 293 ps = - 1193 ps and

tLZ(DQ),max(derated) = 450 ps + 272 ps = + 722 ps.

41. When the device is operated with input clock jitter, this parameter needs to be derated by the actual tJIT(per) of the input clock. (output deratings are

relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-667 SDRAM has tJIT(per),min = - 72 ps and tJIT(per),max = + 93 ps, then tRPRE,min(derated) =

tRPRE,min + tJIT(per),min = 0.9 x tCK(avg) - 72 ps = + 2178 ps and tRPRE,max(derated) = tRPRE,max + tJIT(per),max = 1.1 x tCK(avg) + 93 ps =

+ 2843 ps.

42. When the device is operated with input clock jitter, this parameter needs to be derated by the actual tJIT(duty) of the input clock. (output deratings are

relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-667 SDRAM has tJIT(duty),min = - 72 ps and tJIT(duty),max = + 93 ps, then tRPST,min(derated) =

tRPST,min + tJIT(duty),min = 0.4 x tCK(avg) - 72 ps = + 928 ps and tRPST,max(derated) = tRPST,max + tJIT(duty),max = 0.6 x tCK(avg) + 93 ps = +

1592 ps.

43. When the device is operated with input clock jitter, this parameter needs to be derated by { - tJIT(duty),max - tERR(6-10per),max } and { -

tJIT(duty),min - tERR(6-10per),min } of the actual input clock. (output deratings are relative to the SDRAM input clock.)

For example, if the measured jitter into a DDR2-667 SDRAM has tERR(6-10per),min = - 272 ps, tERR(6- 10per),max = + 293 ps, tJIT(duty),min = -

106 ps and tJIT(duty),max = + 94 ps, then tAOF,min(derated) = tAOF,min + { - tJIT(duty),max - tERR(6-10per),max } = - 450 ps + { - 94 ps - 293 ps} =

- 837 ps and tAOF,max(derated) = tAOF,max + { - tJIT(duty),min - tERR(6-10per),min } = 1050 ps + { 106 ps + 272 ps } = + 1428 ps.

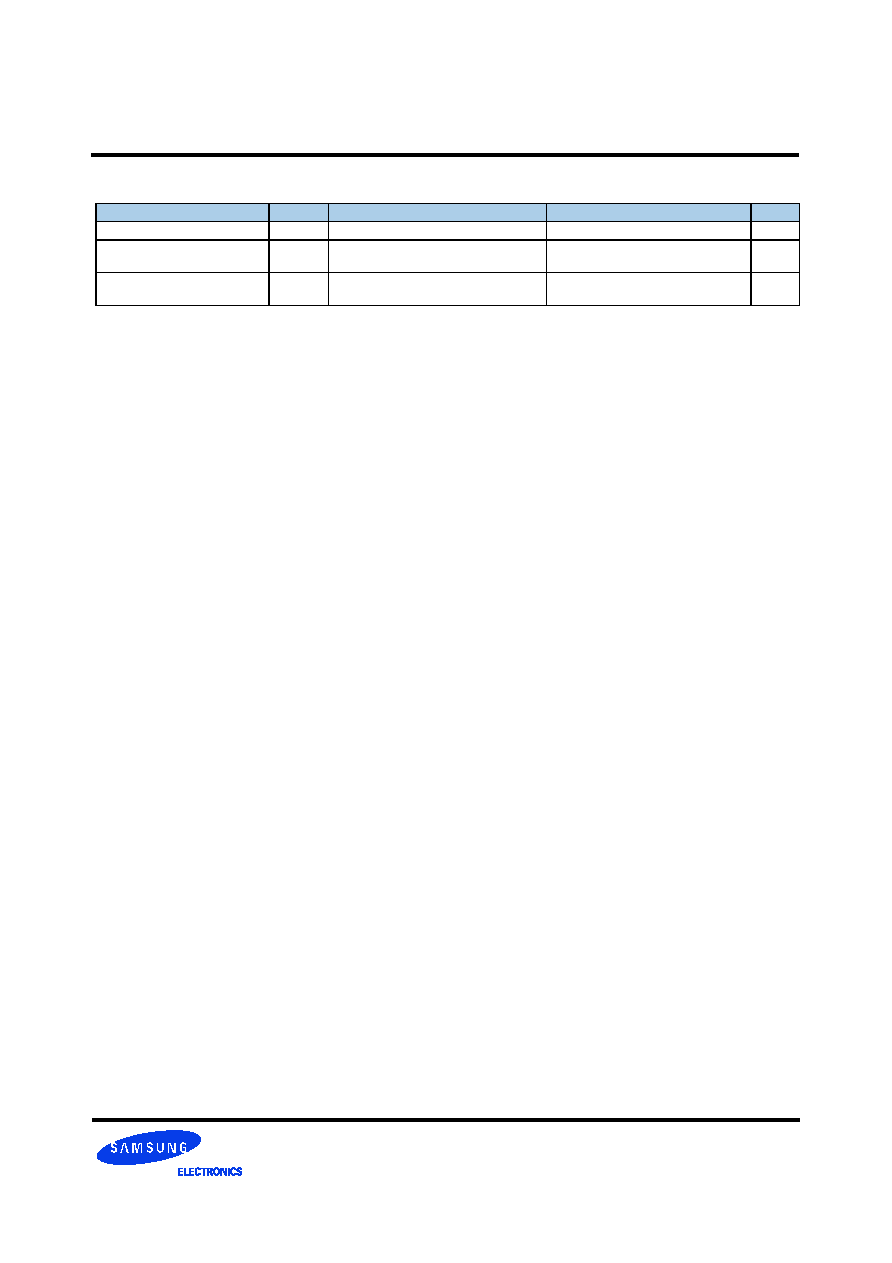

Parameter

Symbol

Min

Max

Units

Absolute clock Period

tCK(abs)

tCK(avg),min + tJIT(per),min

tCK(avg),max + tJIT(per),max

ps

Absolute clock HIGH pulse width

tCH(abs)

tCH(avg),min x tCK(avg),min +

tJIT(duty),min

tCH(avg),max x tCK(avg),max +

tJIT(duty),max

ps

Absolute clock LOW pulse width

tCL(abs)

tCL(avg),min x tCK(avg),min +

tJIT(duty),min

tCL(avg),max x tCK(avg),max +

tJIT(duty),max

ps

相关PDF资料 |

PDF描述 |

|---|---|

| K5A3240YT | Multi-Chip Package MEMORY 32M Bit (4Mx8/2Mx16) Dual Bank NOR Flash Memory / 4M(512Kx8/256Kx16) Full CMOS SRAM |

| K6R1004C1C | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I10 | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I12 | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

相关代理商/技术参数 |

参数描述 |

|---|---|

| K4T56163QN | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:Consumer Memory |

| K4T56163QN-HCE6000 | 制造商:Samsung SDI 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin FBGA Tray |

| K4T56163QN-HCE6T00 | 制造商:Samsung SDI 功能描述: |

| K4T56163QN-ZCE6T00 | 制造商:Samsung 功能描述:256 SDRAM X16 - Tape and Reel |

| K4T56163QN-ZCE7000 | 制造商:Samsung 功能描述:DDR2 SDRAM 32MX16 47H32M16 PBF FBGA 1.8V PLASTIC 512M - Trays |

发布紧急采购,3分钟左右您将得到回复。