- 您现在的位置:买卖IC网 > PDF目录187165 > MT46V32M8P-75ELIT:G 64M X 8 DDR DRAM, 0.75 ns, PDSO66 PDF资料下载

参数资料

| 型号: | MT46V32M8P-75ELIT:G |

| 元件分类: | DRAM |

| 英文描述: | 64M X 8 DDR DRAM, 0.75 ns, PDSO66 |

| 封装: | 0.40 INCH, LEAD FREE,PLASTIC, TSOP-66 |

| 文件页数: | 52/93页 |

| 文件大小: | 3632K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

PDF: 09005aef80768abb/Source: 09005aef82a95a3a

Micron Technology, Inc., reserves the right to change products or specifications without notice.

DDR_x4x8x16_Core2.fm - 256Mb DDR: Rev. O, Core DDR: Rev. B 1/09 EN

54

2003 Micron Technology, Inc. All rights reserved.

256Mb: x4, x8, x16 DDR SDRAM

Operations

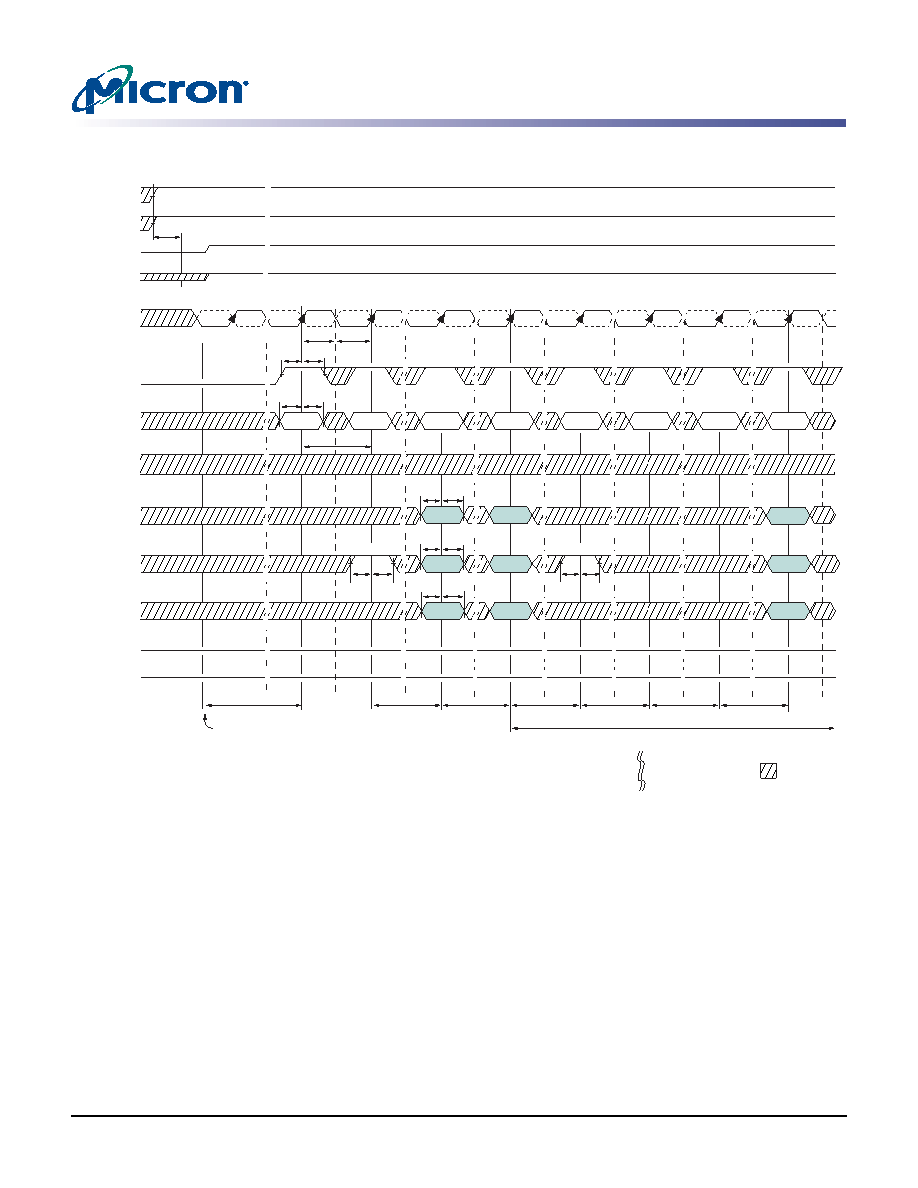

Figure 22:

INITIALIZATION Timing Diagram

Notes:

1. VTT is not applied directly to the device; however, tVTD

≥ 0 to avoid device latch-up. VDDQ,

VTT, and VREF

≤ VDD + 0.3V. Alternatively, VTT may be 1.35V maximum during power-up,

even if VDD/VDDQ are 0V, provided a minimum of 42

Ω of series resistance is used between

the VTT supply and the input pin. Once initialized, VREF must always be powered within the

specified range.

2. Although not required by the Micron device, JEDEC specifies issuing another LMR command

(A8 = 0) prior to activating any bank. If another LMR command is issued, the same, previ-

ously issued operating parameters must be used.

3. The two AUTO REFRESH commands at Td0 and Te0 may be applied following the LMR com-

mand at Ta0.

4. tMRD is required before any command can be applied (during MRD time only NOPs or

DESELECTs are allowed), and 200 cycles of CK are required before a READ command can be

issued.

5. While programming the operating parameters, reset the DLL with A8 = 1.

tVTD1

CKE

LVCMOS

LOW level

DQ

BA0, BA1

200 cycles of CK4

Load extended

mode register

Load mode

register5

tMRD

tRP

tRFC

tIS

Power-up: VDD and CK stable

T = 200s

High-Z

tIH

DM

DQS

High-Z

Address

RA

A10

All banks

CK

CK#

tCH

tCL

tCK

VTT1

VREF

VDD

VDDQ

Command

LMR

NOP

PRE

LMR

AR

ACT2

tIS tIH

BA0 = 1

BA1 = 0

tIS tIH

BA0 = 0

BA1 = 0

tIS tIH

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

Code

tIS tIH

Code

Code3

PRE

All banks

tIS tIH

T0

T1

Ta0

Tb0

Tc0

Td0

Te0

Tf0

(

)

(

)

Don’t Care

BA

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

tRP

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

RA

Indicates A Break in

Time Scale

相关PDF资料 |

PDF描述 |

|---|---|

| MT47H128M4CC-3:B | 128M X 4 DDR DRAM, 0.45 ns, PBGA84 |

| MT47H32M16HR-37EAT:G | 32M X 16 DDR DRAM, 0.5 ns, PBGA84 |

| MT47H64M16BT-3ELIT:A | 64M X 16 DDR DRAM, 0.45 ns, PBGA92 |

| MT47H64M8B6-3ELAT:D | DDR DRAM, PBGA60 |

| MT48H32M16LFCJ-8 | 32M X 16 SYNCHRONOUS DRAM, 7 ns, PBGA54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT46V32M8T66ADC1 | 制造商:Micron Technology Inc 功能描述:32MX8 DDR SDRAM DIE-COM COMMERCIAL 2.5V - Trays |

| MT46V32M8TG-5B/G | 制造商:Micron Technology Inc 功能描述:DRAM Chip DDR SDRAM 256M-Bit 32Mx8 2.6V 66-Pin TSOP Tray |

发布紧急采购,3分钟左右您将得到回复。