- 您现在的位置:买卖IC网 > PDF目录299575 > OR3T307S240-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 196 CLBS, 48000 GATES, PQFP240 PDF资料下载

参数资料

| 型号: | OR3T307S240-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| 封装: | PLASTIC, SQFP-240 |

| 文件页数: | 126/203页 |

| 文件大小: | 1368K |

| 代理商: | OR3T307S240-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页当前第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页

Lattice Semiconductor

29

Data Sheet

November 2006

ORCA Series 3C and 3T FPGAs

Programmable Logic Cells (continued)

Inter-PLC Routing Resources

The inter-PLC routing is used to route signals between

PLCs. The routing segments occur in groups of ten,

and differ in the numbers of PLCs spanned. The x1

routing segments span one PLC, the x5 routing seg-

ments span ve PLCs, the xH routing segments span

one-half the width (height) of the PLC array, and the xL

routing segments span the width (height) of the PLC

array. All types of routing segments run in both horizon-

tal and vertical directions.

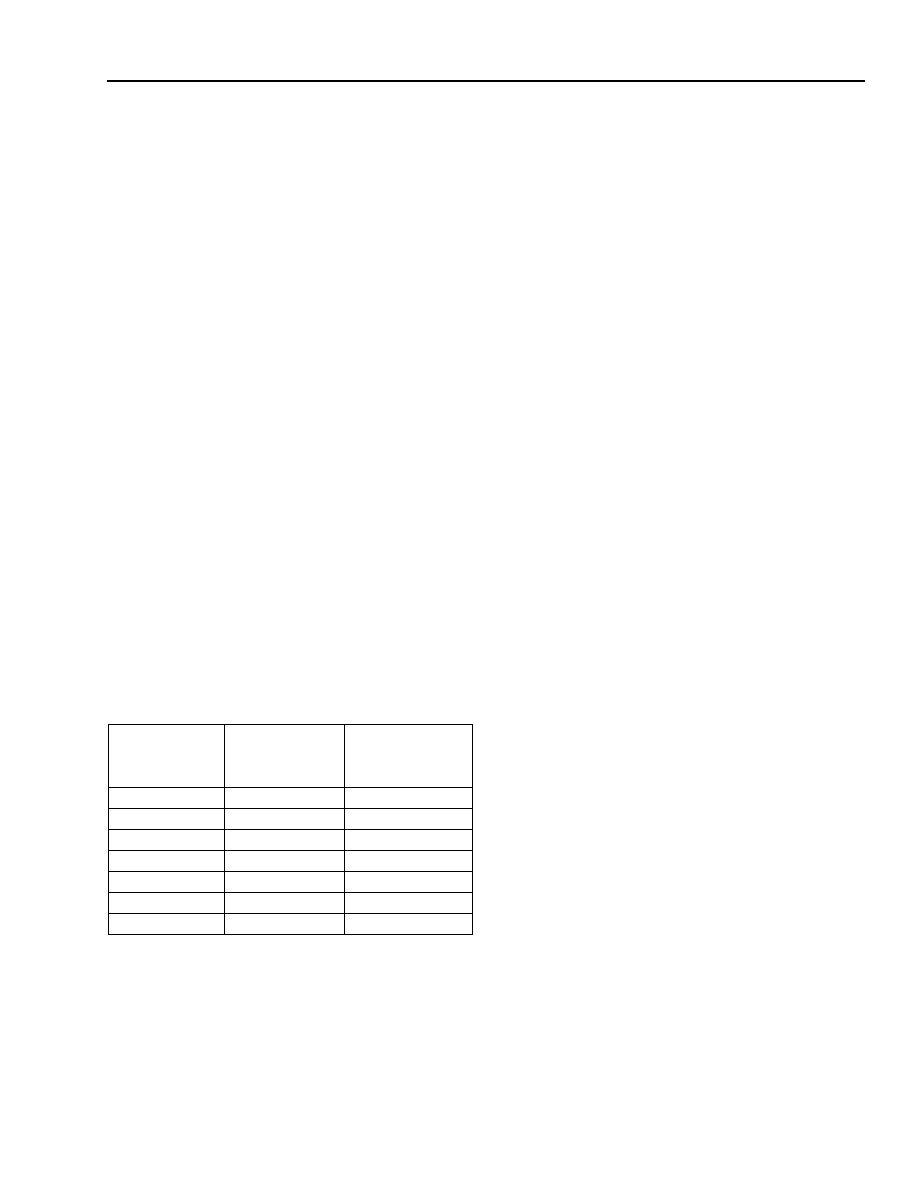

Table 8 shows the groups of inter-PLC routing seg-

ments in each PLC. In the table, there are two rows/col-

umns for x1 lines. They are differentiated by a T for top,

B for bottom, L for left, and R for right. In the ispLEVER

design editor representation, the horizontal x1 routing

segments are located above and below the PFU. The

two groups of vertical segments are located on the left

side of the PFU. The xL and x5 routing segments only

run below and to the left of the PFU, while the xH seg-

ments only run above and to the right of the PFU. The

indexes specify individual routing segments within a

group. For example, the vx5[2] segment runs vertically

to the left of the PFU, spans ve PLCs, and is the third

line in the 10-bit wide group.

PLCs are arranged like tiles on the

ORCA device.

Breaks in routing occur at the middle of the tile (e.g., x1

lines break in the middle of each PLC) and run across

tiles until the next break.

Figure 20 provides a global view of inter-PLC routing

resources across multiple PLCs.

x1 Routing Segments. There are a total of 40 x1 rout-

ing segments per PLC: 20 vertical and 20 horizontal.

Each of these are subdivided into two, 10-bit wide

buses: hx1T[9:0], hx1B[9:0], vx1L[9:0], and vx1R[9:0].

An x1 segment is one PLC long. If a signal net is longer

than one PLC, an x1 segment can be lengthened to n

times its length by turning on n – 1 CIPs. A signal is

routed onto an x1 route segment via the switching rout-

ing segments or BIDI routing segments which also

allows the x1 route segment to be connected to other

inter-PLC segments of different lengths. Corner turning

between x1 segments is provided through direct con-

nections, xSW segments, and xBID segments.

x5 Routing Segments. There are two sets of ten x5

routing segments per PLC. One set (vx5[9:0]) runs ver-

tically, and the other (hx5[9:0]) runs horizontally. Each

x5 segment traverses ve PLCs before it is broken by a

CIP. Two x5 segments in each group break in each

PLC. The two that break are in an equivalent pair; for

example, x5[0] and x5[4]. The x5 segments that break

shift by one at the next PLC. For example, if hx5[0] and

hx5[4] are broken at the current PLC, hx5[1] and hx5[5]

will be broken at the PLC to the right of the current

PLC. There are direct connections to the BIDI routing

segments in the PLC at which the x5 segments break,

on both sides of the break. Signal corner turning is

enabled by CIPs in each PLC that allow the broken x5

segments to directly connect to the broken x5 seg-

ments that run in the orthogonal direction. x5 corner

turning can also be accomplished via the xSW and

xBID segments in a PLC. In addition, the x5 segments

are connected to the FINS and PFU outputs on a bit-

by-bit basis by the xSW segments. x5 segments can be

connected for signal runs in multiples of ve PLCs, or

they can be combined with x1 and xH routing segments

for runs of varying distances.

Table 8. Inter-PLC Routing Resources

Horizontal

Routing

Segments

Vertical

Routing

Segments

Distance

Spanned

hx1U[9:0]

vx1R[9:0]

One PLC

hx1B[9:0]

vx1L[9:0]

One PLC

hx5[9:0]

vx5[9:0]

Five PLCs

hx5[9:0]

vx5[9:0]

Five PLCs

hxL[9:0]

vxL[9:0]

PLC Array

hxH[9:0]

vxH[9:0]

1/2 PLC Array

hCLK

vCLK

PLC Array

Select

devices

have

been

discontinued.

See

Ordering

Information

section

for

product

status.

相关PDF资料 |

PDF描述 |

|---|---|

| OR3T556PS240-DB | FPGA, 324 CLBS, 80000 GATES, PQFP240 |

| OR3T806PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T807PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T55-4BA256I | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

| OR3T55-4BA256 | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR3T30-7S240I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55 | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T55-4BA256I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS208I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS240I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。