- 您现在的位置:买卖IC网 > PDF目录299575 > OR3T307S240-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 196 CLBS, 48000 GATES, PQFP240 PDF资料下载

参数资料

| 型号: | OR3T307S240-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| 封装: | PLASTIC, SQFP-240 |

| 文件页数: | 138/203页 |

| 文件大小: | 1368K |

| 代理商: | OR3T307S240-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页当前第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页

4

Lattice Semiconductor

Data Sheet

November 2006

ORCA Series 3C and 3T FPGAs

System-Level Features

System-level features reduce glue logic requirements

and make a system on a chip possible. These features

in the

ORCA Series 3 include:

■ Full PCI local bus compliance.

■ Dual-use microprocessor interface (MPI) can be

used for conguration, readback, device control, and

device status, as well as for a general-purpose inter-

face to the FPGA. Glueless interface to

i960* and

PowerPC processors with user-congurable

address space provided.

■ Parallel readback of conguration data capability with

the built-in microprocessor interface.

■ Programmable clock manager (PCM) adjusts clock

phase and duty cycle for input clock rates from

5 MHz to 120 MHz. The PCM may be combined with

FPGA logic to create complex functions, such as dig-

ital phase-locked loops (DPLL), frequency counters,

and frequency synthesizers or clock doublers. Two

PCMs are provided per device.

■ True, internal, 3-state, bidirectional buses with simple

control provided by the SLIC.

■ 32 x 4 RAM per PFU, congurable as single- or dual-

port at >176 MHz. Create large, fast RAM/ROM

blocks (128 x 8 in only eight PFUs) using the SLIC

decoders as bank drivers.

*

i960 is a registered trademark of Intel Corporation.

PowerPC is a registered trademark of International Business

Machines Corporation.

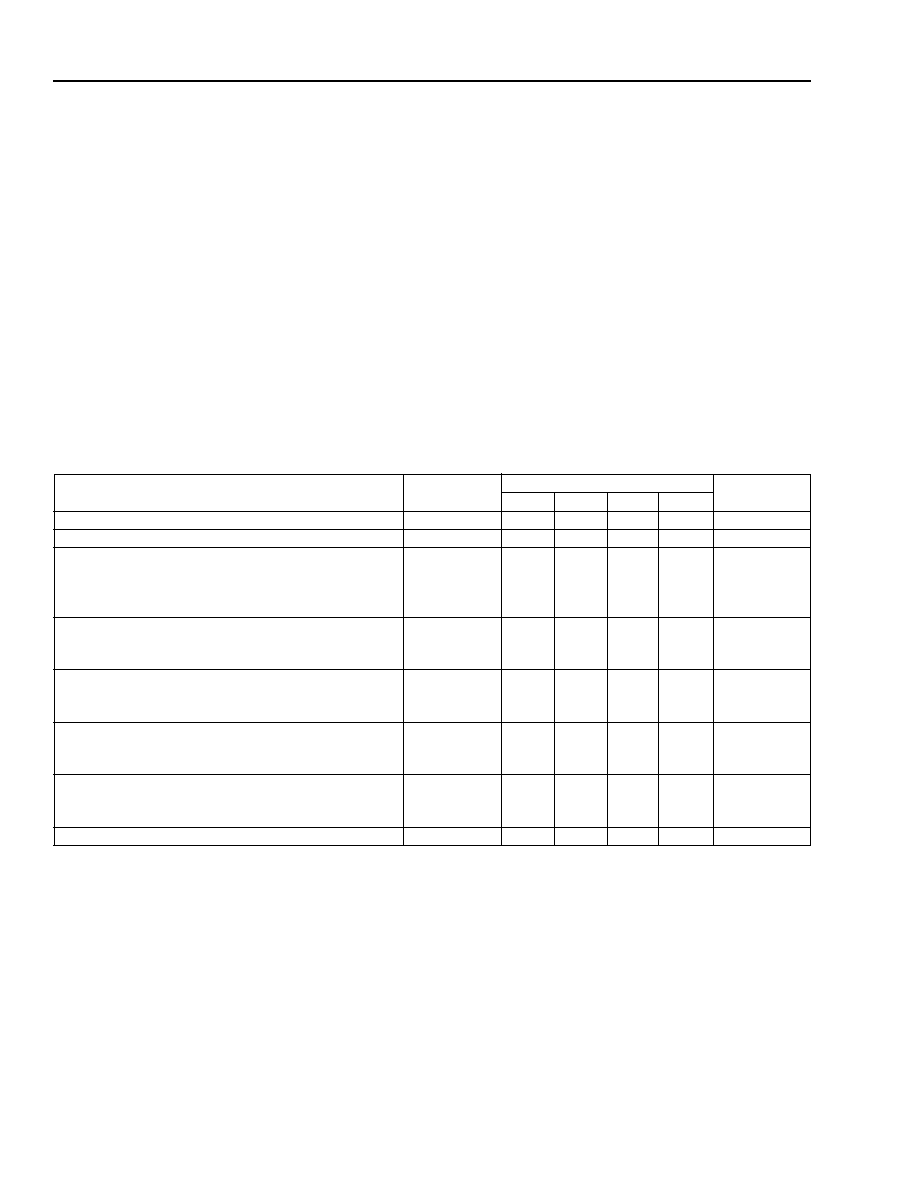

Table 2.

ORCA Series 3 System Performance

1. Implemented using 8 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2. Implemented using two 32 x 12 ROMs and one 12-bit adder, one 8-bit input, one xed operand, one 16-bit output.

3. Implemented using 8 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (7 of 15 PFUs contain only pipelining registers).

4. Implemented using 32 x 4 RAM mode with read data on 3-state buffer to bidirectional read/write bus.

5. Implemented using 32 x 4 dual-port RAM mode.

6. Implemented in one partially occupied SLIC with decoded output set up to CE in same PLC.

7. Implemented in ve partially occupied SLICs.

Parameter

# PFUs

Speed

Unit

-4

-5

-6

-7

16-bit Loadable Up/Down Counter

2

78

102

131

168

MHz

16-bit Accumulator

2

78

102

131

168

MHz

8 x 8 Parallel Multiplier:

Multiplier Mode, Unpipelined1

ROM Mode, Unpipelined2

Multiplier Mode, Pipelined3

11.5

8

15

19

51

76

25

66

104

30

80

127

38

102

166

MHz

32 x 16 RAM (synchronous):

Single-port, 3-state Bus4

Dual-port5

4

97

127

166

151

203

192

253

MHz

128 x 8 RAM (synchronous):

Single-port, 3-state Bus4

Dual-port5

8

88

116

139

176

MHz

8-bit Address Decode (internal):

Using Softwired LUTs

Using SLICs6

0.25

0

4.87

2.35

3.66

1.82

2.58

1.23

2.03

0.99

ns

32-bit Address Decode (internal):

Using Softwired LUTs

Using SLICs7

2

0

16.06

6.91

12.07

5.41

9.01

4.21

7.03

3.37

ns

36-bit Parity Check (internal)

2

16.06

12.07

9.01

7.03

ns

Select

devices

have

been

discontinued.

See

Ordering

Information

section

for

product

status.

相关PDF资料 |

PDF描述 |

|---|---|

| OR3T556PS240-DB | FPGA, 324 CLBS, 80000 GATES, PQFP240 |

| OR3T806PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T807PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T55-4BA256I | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

| OR3T55-4BA256 | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR3T30-7S240I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55 | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T55-4BA256I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS208I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS240I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。