- 您现在的位置:买卖IC网 > PDF目录296800 > PEF22508E (INFINEON TECHNOLOGIES AG) DATACOM, PCM TRANSCEIVER, PBGA256 PDF资料下载

参数资料

| 型号: | PEF22508E |

| 厂商: | INFINEON TECHNOLOGIES AG |

| 元件分类: | 数字传输电路 |

| 英文描述: | DATACOM, PCM TRANSCEIVER, PBGA256 |

| 封装: | 17 X 17 MM, 1 MM PITCH, PLASTIC, LBGA-256 |

| 文件页数: | 115/193页 |

| 文件大小: | 10683K |

| 代理商: | PEF22508E |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页当前第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页

OctalLIU

TM

PEF 22508 E

Pin Descriptions

Data Sheet

28

Rev. 1.0, 2005-06-02

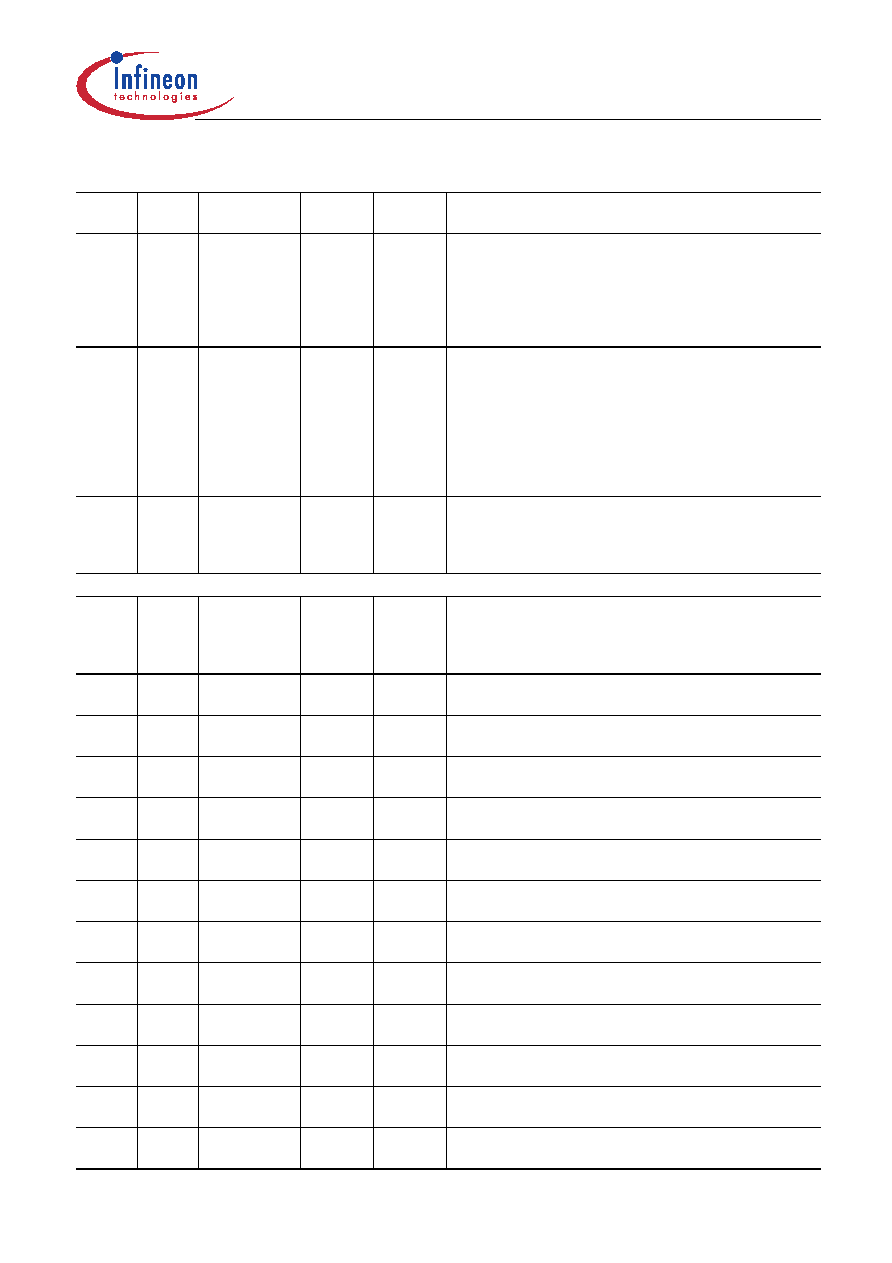

J6

MCLK

I

–

Master Clock

A reference clock of better than ±32 ppm accuracy in

the range of 1.02 to 20 MHz must be provided on this

pin. The OctalLIU

TM internally derives all necessary

clocks from this master

(see registers GCM(6:1)).

G13

SYNC

I

PU

Clock Synchronization of DCO-R

If a clock is detected on pin SYNC the

DCO-R circuitry of the OctalLIU

TM synchronizes to this

1.544/2.048 MHz clock (see LIM0.MAS, CMR1.DCS

and CMR2.DCF). Additionally, in master mode the

OctalLIU

TM is able to synchronize to an 8 kHz reference

clock (IPC.SSYF = 1). If not connected, an internal

pull-up transistor ensures high input level.

G12

FSC

O

–

8 kHz Frame Synchronization

The optionally synchronization pulse is active high or

low for one 2.048/1.544 MHz cycle (pulse width =

488 ns for E1and 648 ns or T1/J1).

Digital (Framer) Interface Receive

C2

RDO1

O

–

Receive Data Out, port 1

Received data at RL1, RL2 is sent to RDOP, RDON.

Clocking of data is done with the rising or falling edge of

RCLK.

C1

FCLKR1

I/O

PU

Framer Data Clock Receive, port 1

Input if PC5.CSRP = 0, output if PC5.CSRP = 1.

E4

RDO2

O

–

Receive Data Out, port 2

See description of RDOP1.

E1

FCLKR2

I/O

PU

Framer Data Clock Receive, port 2

See description of FCLKR1.

L6

RDO3

O

–

Receive Data Out, port 3

See description of RDOP1.

K4

FCLKR3

I/O

PU

Framer Data Clock Receive, port 3

See description of FCLKR1.

M3

RDO4

O

–

Receive Data Out, port 4

See description of RDOP1.

M1

FCLKR4

I/O

PU

Framer Data Clock Receive, port 4

See description of FCLKR1.

P15

RDO5

O

–

Receive Data Out, port 5

See description of RDOP1.

P16

FCLKR5

I/O

PU

Framer Data Clock Receive, port 5

See description of FCLKR1.

M10

RDO6

O

–

Receive Data Out, port 6

See description of RDOP1.

M16

FCLKR6

I/O

PU

Framer Data Clock Receive, port 6

See description of FCLKR1.

F15

RDO7

O

–

Receive Data Out, port 7

See description of RDOP1.

Table 1

I/O Signals (cont’d)

Pin No. Ball

No.

Name

Pin Type Buffer

Type

Function

相关PDF资料 |

PDF描述 |

|---|---|

| PEF22554E | DATACOM, FRAMER, PBGA160 |

| PEF22554HT | DATACOM, FRAMER, PQFP144 |

| PES12-42S-N0024 | |

| PESD3V3V4UK,132 | 25 W, UNIDIRECTIONAL, 4 ELEMENT, SILICON, TVS DIODE |

| PF38F3050L0YUQ3A | SPECIALTY MEMORY CIRCUIT, PBGA88 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PEF22508EV1.1-G | 功能描述:网络控制器与处理器 IC T/E RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| PEF22508EV11G | 制造商:Rochester Electronics LLC 功能描述: 制造商:Infineon Technologies AG 功能描述: |

| PEF22508EV11GXP | 制造商:Lantiq 功能描述:LINE INTERFACE UNITS |

| PEF22508EV11GXT | 制造商:Lantiq 功能描述:LINE INTERFACE UNITS |

| PEF22509EV1.1 | 制造商:Infineon Technologies AG 功能描述:SP000205605_T/E ASIC_TY_PB |

发布紧急采购,3分钟左右您将得到回复。