- 您现在的位置:买卖IC网 > PDF目录296935 > QL1P100-7PUN86C (QUICKLOGIC CORP) FPGA, 640 CLBS, 100000 GATES, PBGA86 PDF资料下载

参数资料

| 型号: | QL1P100-7PUN86C |

| 厂商: | QUICKLOGIC CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

| 封装: | 6 X 6 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, LEAD FREE, TFBGA-86 |

| 文件页数: | 3/44页 |

| 文件大小: | 1101K |

| 代理商: | QL1P100-7PUN86C |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

2010 QuickLogic Corporation

QuickLogic PolarPro Device Data Sheet — 86-Pin TFBGA QL1P100 Rev. G

11

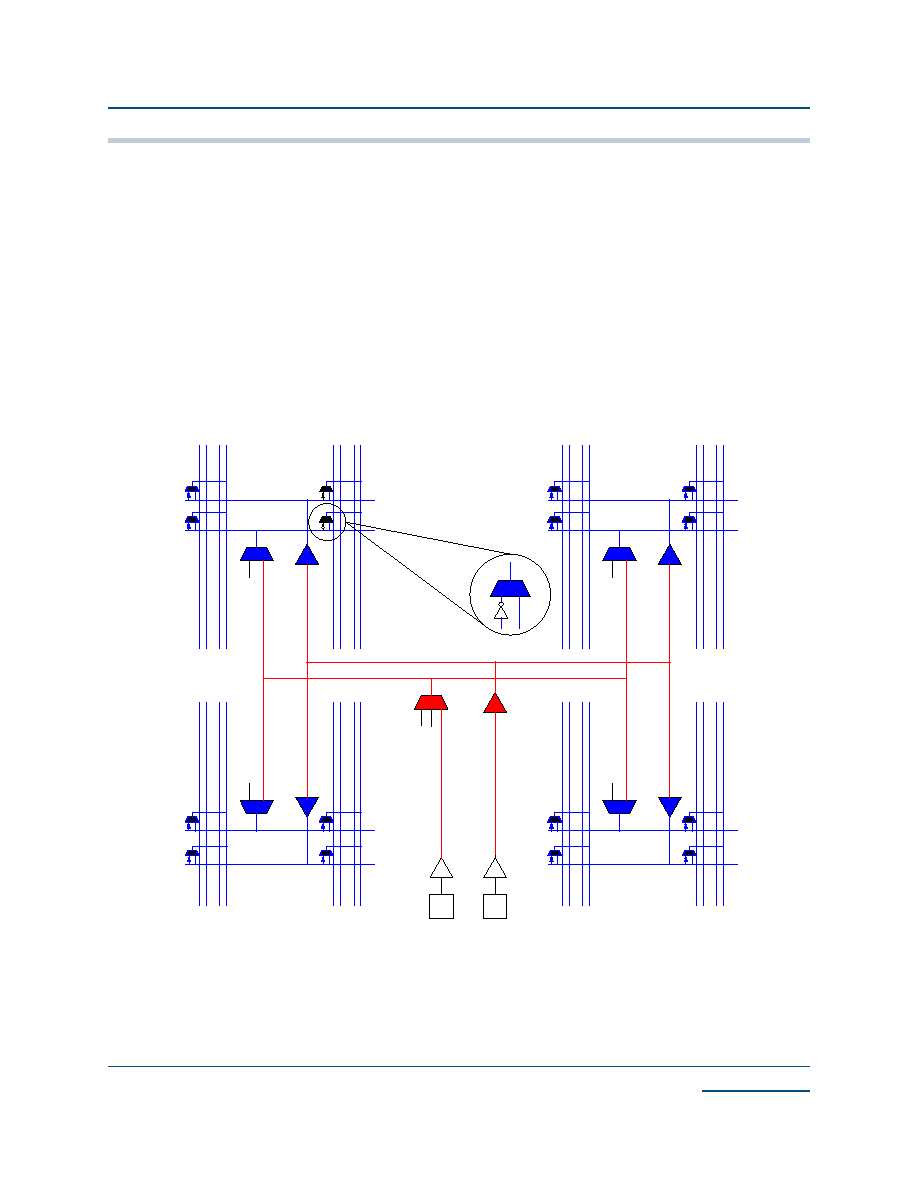

86-Pin TFBGA QL1P100 Clock Network Architecture

Clock Network Architecture

The PolarPro clock network architecture consists of a 2-level H-tree network as shown in Figure 9. The first

level of each clock tree (high-lighted in red) spans from the clock input pad to the global clock network and to

the center of each quadrant of the chip. The second level (high-lighted in blue) spans from the quadrant clock

network to every logic cell inside that quadrant. There are five global clocks in the global clock network, and

five quadrant clocks in each quadrant clock network. All global clocks drive the quadrant clock network inputs.

The quadrant clocks output to clock inversion muxes, which pass either the original input clock or an inverted

version of the input clock to the logic cells in that quadrant. The global clocks can drive RAM block clock inputs

and reset, set, enable, and clock inputs to I/O registers. Furthermore, the quadrant clock outputs can be routed

to all logic cell inputs.

Figure 9: PolarPro Clock Architecture

Of the five global clock networks, four can be either driven directly by clock pads, Configurable Clock Manager

(CCM) outputs, or internally generated signals. These four global clocks go through 3-input global clock muxes

located in the middle of the die. See Figure 10 for a diagram of a 3-input global clock mux. The fifth is a

dedicated global clock network that goes directly to the quadrant clock network and is used as a dedicated fast

clock.

Quadrant

Clock

Network

Global Clock

Network

x4

Inversion

Mux

Quadrant

Clock

Network

Quadrant

Clock

Network

Quadrant

Clock

Network

相关PDF资料 |

PDF描述 |

|---|---|

| QL1P100-7PUN86I | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

| QL1P100-7PUN86M | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

| QL1P100-8PU86C | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

| QL1P100-8PU86M | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

| QL1P100-8PUN86C | FPGA, 640 CLBS, 100000 GATES, PBGA86 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL-1RED | 制造商:Panduit Corp 功能描述: |

| QL-1WHT | 制造商:Panduit Corp 功能描述: |

| QL-1YEL | 制造商:Panduit Corp 功能描述:B-SI |

| QL2003 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3.3V and 5.0V pASIC-R 2 FPGA Combining Speed, Density, Low Cost and Flexibility |

| QL2003-0PF100C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。