参数资料

| 型号: | XCV405E-6FG676I |

| 厂商: | Xilinx Inc |

| 文件页数: | 30/118页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 676-BGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB数: | 2400 |

| 逻辑元件/单元数: | 10800 |

| RAM 位总计: | 573440 |

| 输入/输出数: | 404 |

| 门数: | 129600 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 676-BGA |

| 供应商设备封装: | 676-FBGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v3.0) March 21, 2014

Module 2 of 4

15

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

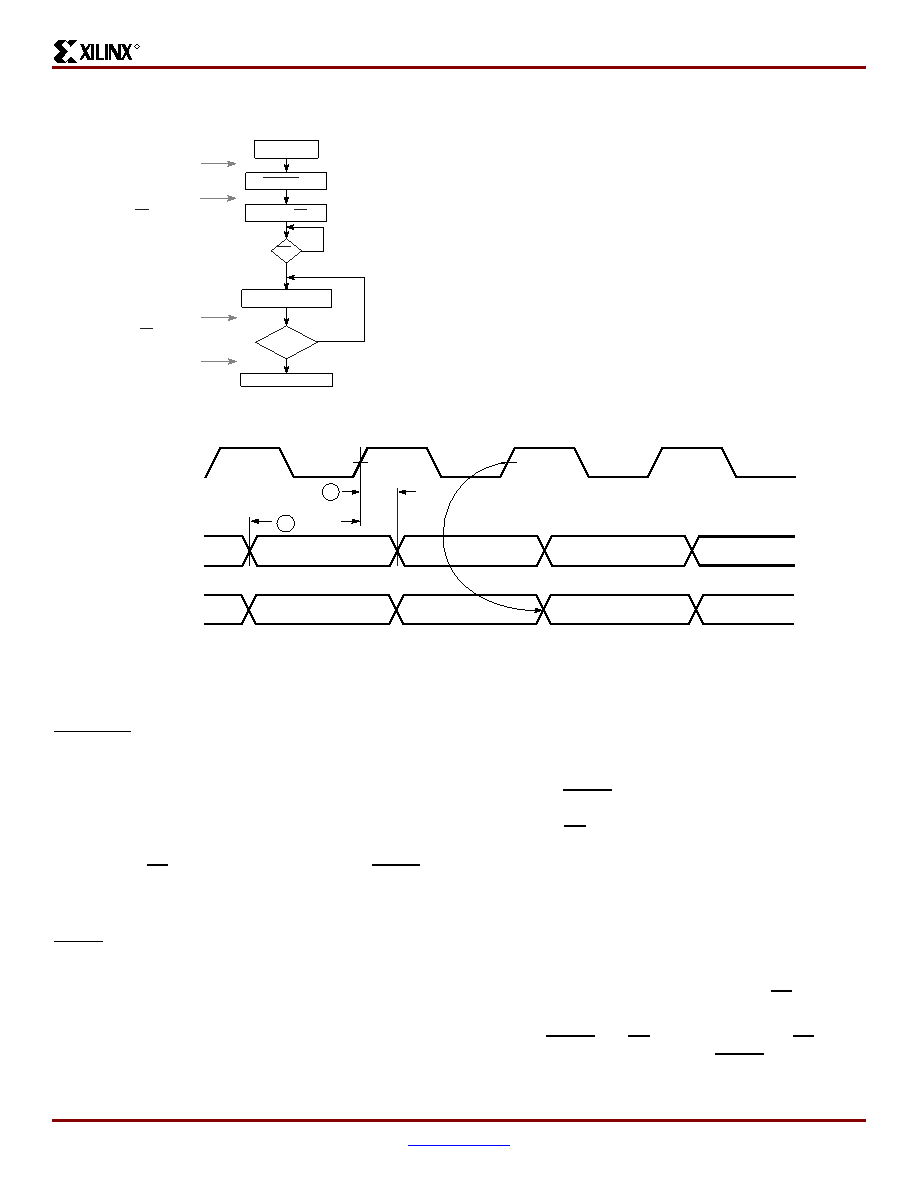

The sequence of operations necessary to configure a

Virtex-E FPGA serially appears in Figure 15.

Figure 16 shows the timing of master-serial configuration.

Master-serial mode is selected by a <000> or <100> on the

mode pins (M2, M1, M0). Table 10 shows the timing infor-

mation for Figure 16

.

At power-up, VCC must rise from 1.0 V to VCC min in less

than 50 ms, otherwise delay configuration by pulling

PROGRAM Low until VCC is valid.

SelectMAP Mode

The SelectMAP mode is the fastest configuration option.

Byte-wide data is written into the FPGA with a BUSY flag

controlling the flow of data.

An external data source provides a byte stream, CCLK, a

Chip Select (CS) signal and a Write signal (WRITE). If

BUSY is asserted (High) by the FPGA, the data must be

held until BUSY goes Low.

Data can also be read using the SelectMAP mode. If

WRITE is not asserted, configuration data is read out of the

FPGA as part of a readback operation.

After configuration, the pins of the SelectMAP port can be

used as additional user I/O. Alternatively, the port can be

retained to permit high-speed 8-bit readback.

Retention of the SelectMAP port is selectable on a

design-by-design basis when the bitstream is generated. If

retention is selected, PROHIBIT constraints are required to

prevent SelectMAP-port pins from being used as user I/O.

Multiple Virtex-E FPGAs can be configured using the

SelectMAP mode, and be made to start-up simultaneously.

To configure multiple devices in this way, wire the individual

CCLK, Data, WRITE, and BUSY pins of all the devices in

parallel. The individual devices are loaded separately by

asserting the CS pin of each device in turn and writing the

appropriate data. See Table 11 for SelectMAP Write Timing

Characteristics.

Write

Write operations send packets of configuration data into the

FPGA. The sequence of operations for a multi-cycle write

operation is shown below. Note that a configuration packet

can be split into many such sequences. The packet does

not have to complete within one assertion of CS, illustrated

in Figure 17.

1.

Assert WRITE and CS Low. Note that when CS is

asserted on successive CCLKs, WRITE must remain

Figure 15: Serial Configuration Flowchart

Apply Power

Set PROGRAM = High

Release INIT

If used to delay

configuration

Load a Configuration Bit

High

Low

FPGA makes a final

clearing pass and releases

INIT when finished.

FPGA starts to clear

configuration memory.

ds009_15_111799

Configuration Completed

End of

Bitstream?

Yes

No

Once per bitstream,

FPGA checks data using CRC

and pulls INIT Low on error.

If no CRC errors found,

FPGA enters start-up phase

causing DONE to go High.

INIT?

Figure 16: Master-Serial Mode Programming Switching Characteristics

Serial Data In

CCLK

(Output)

Serial DOUT

(Output)

1 TDSCK

2

TCKDS

DS022_44_071201

相关PDF资料 |

PDF描述 |

|---|---|

| BR93L86RFVM-WTR | IC EEPROM 16KBIT 2MHZ 8MSOP |

| BR93L86RFV-WE2 | IC EEPROM 16KBIT 2MHZ 8SSOP |

| BR25L020FV-WE2 | IC EEPROM SER 2KB SPI BUS 8SSOP |

| BR25L020FVM-WTR | IC EEPROM SER 2KB SPI BUS 8MSOP |

| BR25L020FVJ-WE2 | IC EEPROM 2KBIT 5MHZ 8TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCV405E-6FG900C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-6FG900I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG556C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。