参数资料

| 型号: | XCV405E-6FG676I |

| 厂商: | Xilinx Inc |

| 文件页数: | 67/118页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 676-BGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB数: | 2400 |

| 逻辑元件/单元数: | 10800 |

| RAM 位总计: | 573440 |

| 输入/输出数: | 404 |

| 门数: | 129600 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 676-BGA |

| 供应商设备封装: | 676-FBGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 2 of 4

DS025-2 (v3.0) March 21, 2014

48

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Creating LVDS Output Buffers

LVDS output buffer can be placed in wide number of IOB

locations. The exact location are dependent on the package

that is used. The Virtex-E package information lists the pos-

sible locations as IO_L#P for the P-side and IO_L#N for the

N-side where # is the pair number.

HDL Instantiation

Both output buffers are required to be instantiated in the

design and placed on the correct IO_L#P and IO_L#N loca-

tions. The IOB must have the same net source the following

pins, clock (C), set/reset (SR), output (O), output clock

enable (OCE). In addition, the output (O) pins must be

inverted with respect to each other, and if output registers

are used, the INIT states must be opposite values (one

HIGH and one LOW). Failure to follow these rules leads to

DRC errors in software.

VHDL Instantiation

data0_p

: OBUF_LVDS port map

(I=>data_int(0),

O=>data_p(0));

data0_inv: INV

port map

(I=>data_int(0),

O=>data_n_int(0));

data0_n

: OBUF_LVDS port map

(I=>data_n_int(0), O=>data_n(0));

Verilog Instantiation

OBUF_LVDS data0_p

(.I(data_int[0]),

.O(data_p[0]));

INV

data0_inv (.I(data_int[0],

.O(data_n_int[0]);

OBUF_LVDS data0_n

(.I(data_n_int[0]),

.O(data_n[0]));

Location Constraints

All LVDS buffers must be explicitly placed on a device. For

the output buffers this can be done with the following con-

straint in the UCF or NCF file.

NET data_p<0> LOC = D28; # IO_L0P

NET data_n<0> LOC = B29; # IO_L0N

Synchronous vs. Asynchronous Outputs

If the outputs are synchronous (registered in the IOB), then

any IO_L#P|N pair can be used. If the outputs are asynchro-

nous (no output register), then they must use one of the

pairs that are part of the same IOB group at the end of a

ROW or at the top/bottom of a COLUMN in the device.

The LVDS pairs that can be used as asynchronous outputs

are listed in the Virtex-E pinout tables. Some pairs are

marked as asynchronous-capable for all devices in that

package, and others are marked as available only for that

device in the package. If the device size might change at

some point in the product lifetime, then only the common

pairs for all packages should be used.

Adding an Output Register

All LVDS buffers can have an output register in the IOB. The

output registers must be in both the P-side and N-side IOBs.

All the normal IOB register options are available (FD, FDE,

FDC, FDCE, FDP, FDPE, FDR, FDRE, FDS, FDSE, LD,

LDE, LDC, LDCE, LDP, LDPE). The register elements can

be inferred or explicitly instantiated in the HDL code.

Special care must be taken to insure that the D pins of the

registers are inverted and that the INIT states of the regis-

ters are opposite. The clock pin (C), clock enable (CE) and

set/reset (CLR/PRE or S/R) pins must connect to the same

source. Failure to do this leads to a DRC error in the soft-

ware.

The register elements can be packed in the IOB using the

IOB property to TRUE on the register or by using the “map

-pr [i|o|b]” where “i” is inputs only, “o” is outputs only and “b”

is both inputs and outputs.

To improve design coding times VHDL and Verilog synthe-

sis macro libraries have been developed to explicitly create

these structures. The output library macros are listed in

Table 43. The O and OB inputs to the macros are the exter-

nal net connections.

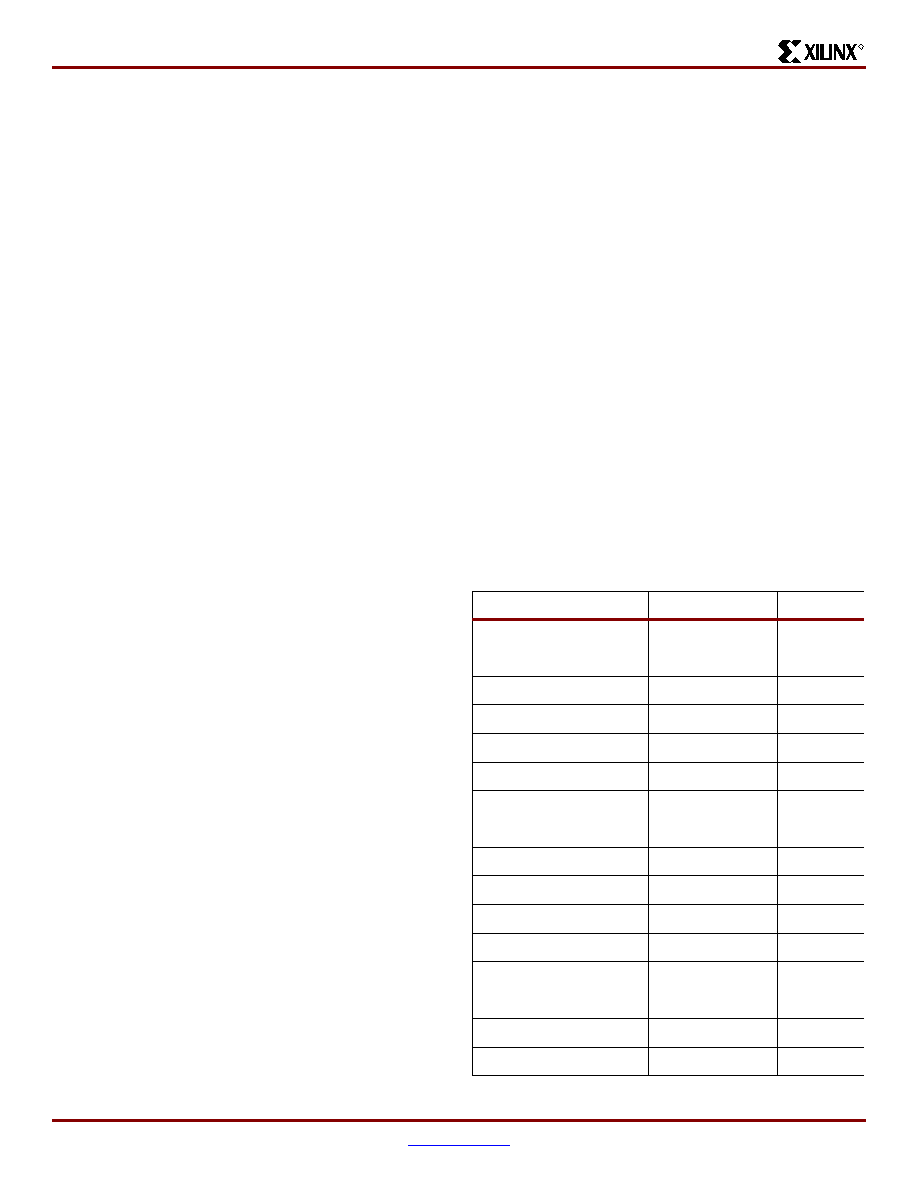

Table 43:

Output Library Macros

Name

Inputs

Outputs

OBUFDS_FD_LVDS

D, C

O, OB

OBUFDS_FDE_LVDS

DD, CE, C

O, OB

OBUFDS_FDC_LVDS

D, C, CLR

O, OB

OBUFDS_FDCE_LVDS

D, CE, C, CLR

O, OB

OBUFDS_FDP_LVDS

D, C, PRE

O, OB

OBUFDS_FDPE_LVDS

D, CE, C, PRE

O, OB

OBUFDS_FDR_LVDS

D, C, R

O, OB

OBUFDS_FDRE_LVDS

D, CE, C, R

O, OB

OBUFDS_FDS_LVDS

D, C, S

O, OB

OBUFDS_FDSE_LVDS

D, CE, C, S

O, OB

OBUFDS_LD_LVDS

D, G

O, OB

OBUFDS_LDE_LVDS

D, GE, G

O, OB

OBUFDS_LDC_LVDS

D, G, CLR

O, OB

OBUFDS_LDCE_LVDS

D, GE, G, CLR

O, OB

OBUFDS_LDP_LVDS

D, G, PRE

O, OB

OBUFDS_LDPE_LVDS

D, GE, G, PRE

O, OB

相关PDF资料 |

PDF描述 |

|---|---|

| BR93L86RFVM-WTR | IC EEPROM 16KBIT 2MHZ 8MSOP |

| BR93L86RFV-WE2 | IC EEPROM 16KBIT 2MHZ 8SSOP |

| BR25L020FV-WE2 | IC EEPROM SER 2KB SPI BUS 8SSOP |

| BR25L020FVM-WTR | IC EEPROM SER 2KB SPI BUS 8MSOP |

| BR25L020FVJ-WE2 | IC EEPROM 2KBIT 5MHZ 8TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCV405E-6FG900C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-6FG900I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG556C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。