- 您现在的位置:买卖IC网 > PDF目录298744 > A42MX24-3VQ100B (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF资料下载

参数资料

| 型号: | A42MX24-3VQ100B |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件页数: | 14/93页 |

| 文件大小: | 854K |

| 代理商: | A42MX24-3VQ100B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

21

Data Device Corporation

www.ddc-web.com

BU-6474X/6484X/6486X

J-07/05-0

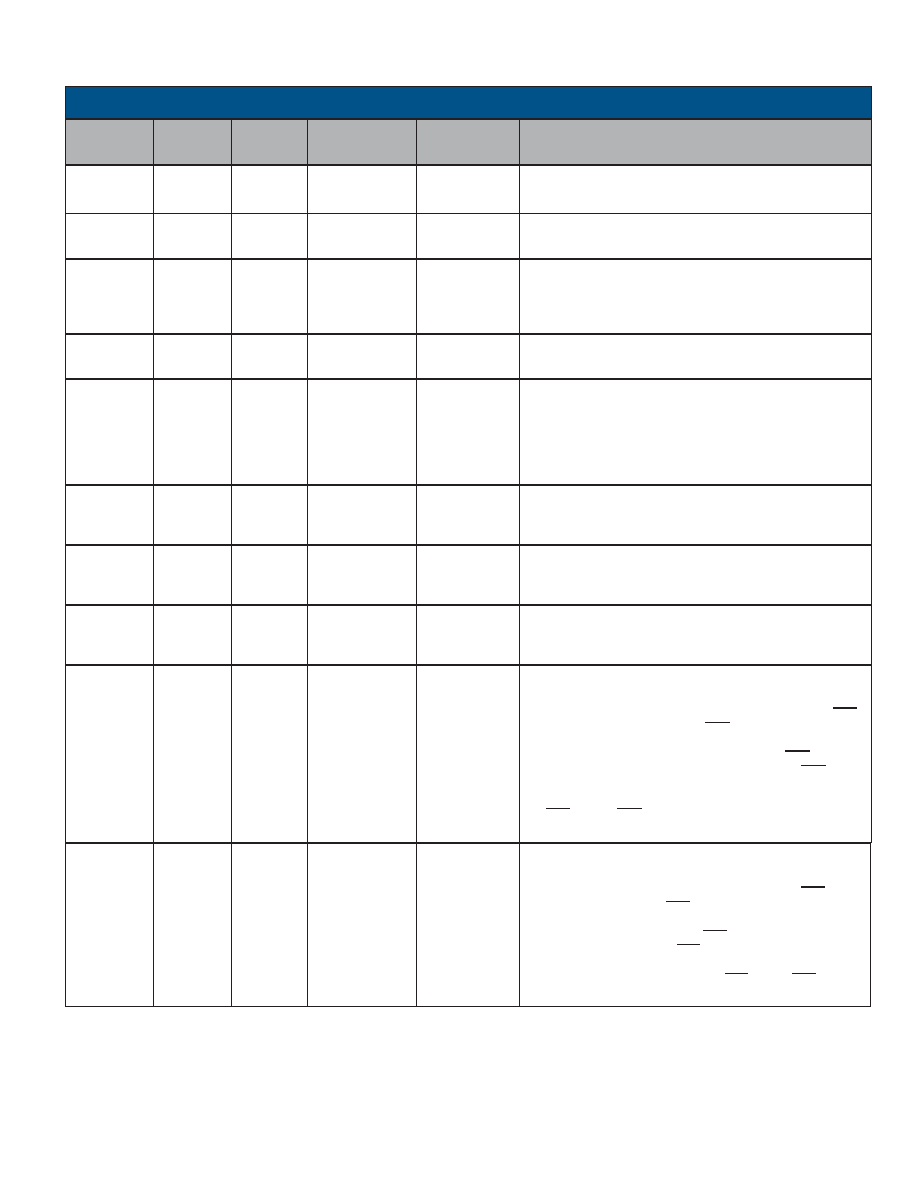

TABLE 36. BC OPERATIONS FOR MESSAGE SEQUENCE CONTROL

INSTRUCTION MNEMONIC

OP CODE

(HEX)

PARAMETER

CONDITIONAL

OR

UNCONDITIONAL

DESCRIPTION

Interrupt

Request

Execute

Message

IRQ

XEQ

0006

0001

Interrupt

Bit Pattern

in 4 LS bits

Message Control /

Status Block

Address

Conditional

(See Note)

Generate an interrupt if the condition flag tests TRUE, otherwise

continue execution at the next OpCode in the instruction list.

The passed parameter (Interrupt Bit Pattern) specifies which of

the ENHANCED BC IRQ bit(s) (bits 5-2) will be set in Interrupt

Status Register #2. Only the four LSBs of the passed parameter

are used. A parameter where the four LSBs are logic "0" will

not generate an interrupt.

Executes the message at the specified Message Control/Status

Block Address if the condition flag tests TRUE, otherwise con-

tinue execution at the next OpCode in the instruction list.

Compare to

Frame Timer

Halt

Jump

CFT

HLT

JMP

000A

0007

0002

Delay Time Value

(Resolution

= 100S / LSB)

Not Used

(Don’t Care)

Instruction List

Address

Unconditional

Conditional

Compare Time Value to Frame Time Counter. The LT/GP0 and

EQ/GP1 flag bits are set or cleared based on the results of the

compare. If the value of the CFT's parameter is less than the

value of the frame time counter, then the LT/GP0 and NE/GP1

flags will be set, while the GT-EQ/GP0 and EQ/GP1 flags will

be cleared. If the value of the CFT's parameter is equal to the

value of the frame time counter, then the GT-EQ/GP0 and

EQ/GP1 flags will be set, while the LT/GP0 and NE/GP1 flags

will be cleared. If the value of the CFT's parameter is greater

than the current value of the frame time counter, then the GT-

EQ/GP0 and NE/GP1 flags will be set, while the LT/GP0 and

EQ/GP1 flags will be cleared.

Stop execution of the Message Sequence Control Program until

a new BC Start is issued by the host if the condition flag tests

TRUE, otherwise continue execution at the next OpCode in the

instruction list.

Jump to the OpCode specified in the Instruction List if the con-

dition flag tests TRUE, otherwise continue execution at the next

OpCode in the instruction list.

Compare to

Message

Timer

Delay

Subroutine

Call

CMT

DLY

CAL

000B

0008

0003

Delay Time Value

(Resolution

= 1S / LSB)

Delay Time Value

(Resolution = 1S

/ LSB)

Instruction List

Address

Unconditional

Conditional

Compare Time Value to Message Time Counter. The LT/GP0 and

EQ/GP1 flag bits are set or cleared based on the results of the

compare. If the value of the CMT's parameter is less than the value

of the message time counter, then the LT/GP0 and NE/GP1 flags

will be set, while the GT-EQ/GP0 and EQ/GP1 flags will be cleared.

If the value of the CMT's parameter is equal to the value of the mes-

sage time counter, then the GT-EQ/GP0 and EQ/GP1 flags will be

set, while the LT/GP0 and NE/GP1 flags will be cleared. If the value

of the CMT's parameter is greater than the current value of the

message time counter, then the GT-EQ/GP0 and NE/GP1 flags will

be set, while the LT/GP0 and EQ/GP1 flags will be cleared.

Delay the time specified by the Time parameter before execut-

ing the next OpCode if the condition flag tests TRUE, otherwise

continue execution at the next OpCode without delay. The delay

generated will use the Time to Next Message Timer.

Jump to the OpCode specified by the Instruction List Address

and push the Address of the Next OpCode on the Call Stack if

the condition flag tests TRUE, otherwise continue execution at

the next OpCode in the instruction list. Note that the maximum

depth of the subroutine call stack is four.

Wait Until

Frame Timer

= 0

Subroutine

Return

WFT

RTN

0009

0004

Not Used

(Don’t Care)

Not Used

(Don’t Care)

Conditional

Wait until Frame Time counter is equal to Zero before continu-

ing execution of the Message Sequence Control Program if the

condition flag tests TRUE, otherwise continue execution at the

next OpCode without delay.

Return to the OpCode popped off the Call Stack if the condition

flag tests TRUE, otherwise continue execution at the next

OpCode in the instruction list.

NOTE: While the XEQ (Execute Message) instruction is conditional, not all condition codes may be used to enable its use. The ALWAYS and NEVER condition codes

may be used. The eight general purpose flag bits, GP0 through GP7, may also be used. However, if GP0 through GP7 are used, it is imperative that the host processor

not modify the value of the specific general purpose flag bit that enabled a particular message while that message is being processed. Similarly, the LT, GT-EQ, EQ, and

NE flags, which the BC only updates by means of the CFT and CMT instructions, may also be used. However, these two flags are dual use. Therefore, if these are used, it

is imperative that the host processor not modify the value of the specific flag (GP0 or GP1) that enabled a particular message while that message is being processed. The

NORESP, FMT ERR, GD BLK XFER, MASKED STATUS SET, BAD MESSAGE, RETRY0, and RETRY1 condition codes are not available for use with the XEQ instruction

and should not be used to enable its execution.

相关PDF资料 |

PDF描述 |

|---|---|

| A42MX36-2PQ100B | 40MX and 42MX FPGA Families |

| A42MX36-2PQ100ES | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100 | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100A | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100B | 40MX and 42MX FPGA Families |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A42MX24-FPL84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPLG84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ208 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQG160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

发布紧急采购,3分钟左右您将得到回复。