- 您现在的位置:买卖IC网 > PDF目录298744 > A42MX24-3VQ100B (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF资料下载

参数资料

| 型号: | A42MX24-3VQ100B |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件页数: | 53/93页 |

| 文件大小: | 854K |

| 代理商: | A42MX24-3VQ100B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

57

Data Device Corporation

www.ddc-web.com

BU-6474X/6484X/6486X

J-07/05-0

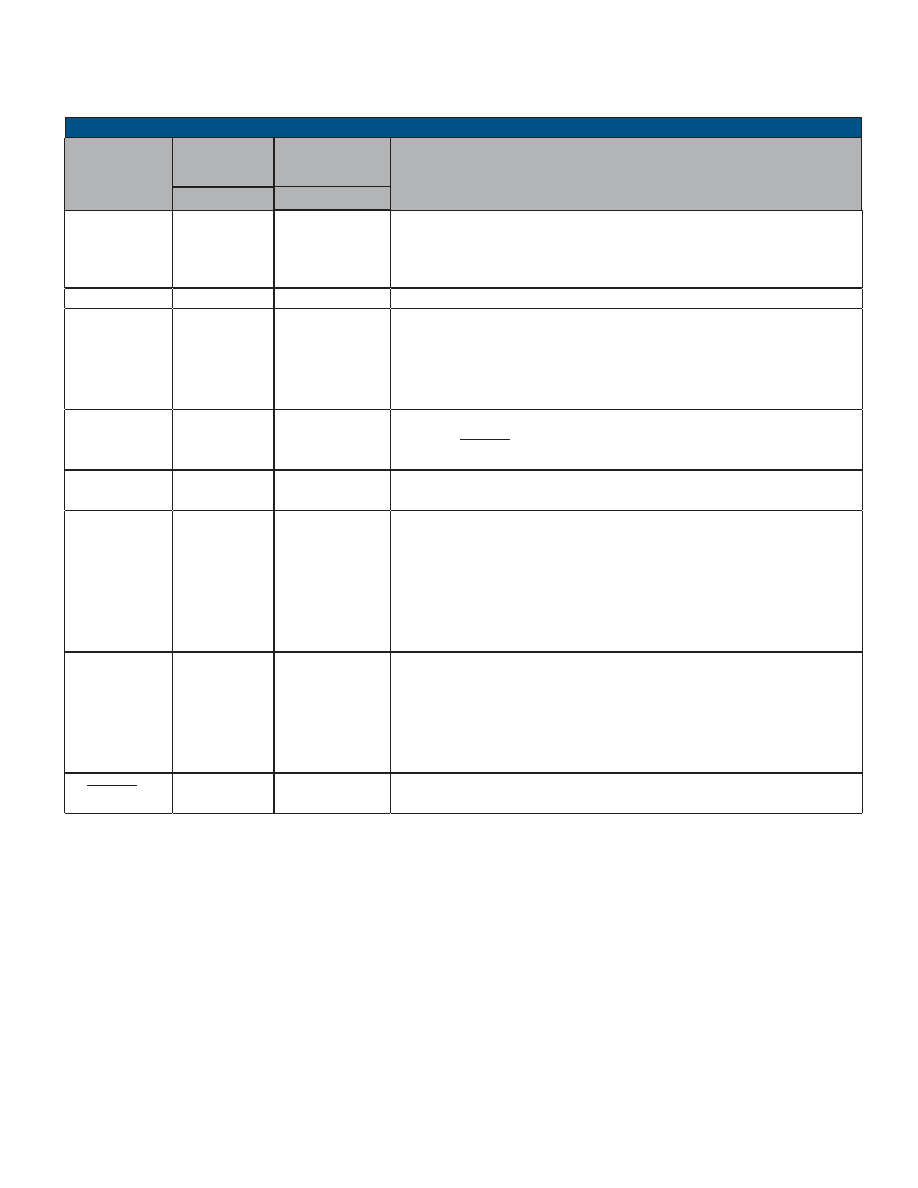

BALL GRID ARRAY PACKAGE - SIGNAL DESCRIPTIONS BY FUNCTIONAL GROUPS

+ 3.3V_Xcvr

-

+ 3.3V_Logic

-

Gnd_Logic

E12, E13, E14,

F12, F13, F14,

G12, G13, G14,

H12, H13, H14,

VDD_Low (I)

A13

TABLE 57. POWER AND GROUND

SIGNAL NAME

BU-64840B3

BU-64860B3

BALL

BU-64743B8

BU-64843B8

BU-64863B8

BALL

+ 3.3 Volt Transceiver Power

+ 5.0V_Xcvr

F1, F2, U13,V13

A4, A5, B4, B5, J1,

J2, J3, J4, J5, K1,

K2, K3, K4, K5, U4,

U5, V4, V5

A8, A9, B8, B9,

L16, L17, M16,

M17, N12, N13,

P12, P13, R6, R7,

T6, T7, U6, U7, V6,

V7

E10, E11, E12,

F10, F11, F12,

G10, G11, G12,

H10, H11, H12,

R11, R12, R13,

T11, T12, T13, U11,

U12, U13

-

+ 5.0 Volt Transceiver Power

+3.3 V Logic Power

+ 5.0V/

+ 3.3V_Logic

A7, L1, L2, L15,

L16, M3, P7, P9,

R9, V8

-

+5.0V/+3.3V Logic Power. These balls may connect to either +5.0V or +3.3V. Refer to

input signal VDD_Low (ball A13) to determine voltage selection options.

+ 5.0V_RAM

P4, R4, (BU-

64860B3 only)

-

For BU-64860B3 this ball must be connected to +5.0V

Gnd_Xcvr/

Thermal

D3, D4, D5, E2, E3,

E4, E5, F3, F4, F5,

G2, G3, G4, G5,

H3, H4, H5, P11,

P12, P13, P14,

P15, R11, R12,

R13, R14, R15,

T11, T12, T13, T14,

T15, U12, U14

D3, D4, D5, E3, E4,

E5, F1, F2, F3, F4,

F5, G3, G4, G5, L3,

L4, L5, M3, M4, M5,

N1, N2, N3, N4, N5,

P3, P4, P5

Transceiver Ground/Thermal connections. See Thermal Management Section for

important user information.

Logic Ground.

Input that selects logic threshold voltage. Set to logic "0" for 3.3V threshold and to

+5V(logic "1") for 5V threshold. Must match "+5.0V/+3V Logic" input voltage.

DESCRIPTION

NOTE: Logic ground and transceiver ground are not tied together inside the package.

相关PDF资料 |

PDF描述 |

|---|---|

| A42MX36-2PQ100B | 40MX and 42MX FPGA Families |

| A42MX36-2PQ100ES | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100 | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100A | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100B | 40MX and 42MX FPGA Families |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A42MX24-FPL84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPLG84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ208 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQG160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

发布紧急采购,3分钟左右您将得到回复。