- 您现在的位置:买卖IC网 > PDF目录166397 > B900J24PXX12I 0-BIT, 80 MHz, OTHER DSP, PQFP44 PDF资料下载

参数资料

| 型号: | B900J24PXX12I |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| 文件页数: | 39/100页 |

| 文件大小: | 1547K |

| 代理商: | B900J24PXX12I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Advance Data Sheet

B900

July 1999

Baseband Signal Processor

Lucent Technologies Inc.

43

5 Software Architecture (continued)

5.1

Instruction Set (continued)

5.1.4 Conditional Mnemonics (Flags)

Please note the following:

s

Testing the state of the counter (c0 or c1) automatically increments the counter by one.

s

The pseudorandom sequence generator (PSG) may be reset by writing any value to the pi register, except

during an interrupt service routine. While in an interrupt service routine, writing to the pi register updates the

register and does not reset the PSG. If not in an interrupt service routine, writing to the pi register resets the

PSG. (The pi register is updated, but written with the contents of the PC on the next instruction.) Interrupts must

be disabled when writing to the pi register. If an interrupt is taken after the pi write, but before pi is updated with

the PC value, the ireturn instruction does not return to the correct location. However, if the RAND bit in the auc

register is set, writing the pi register never resets the PSG. A random rounding function can be implemented with

either heads or tails.

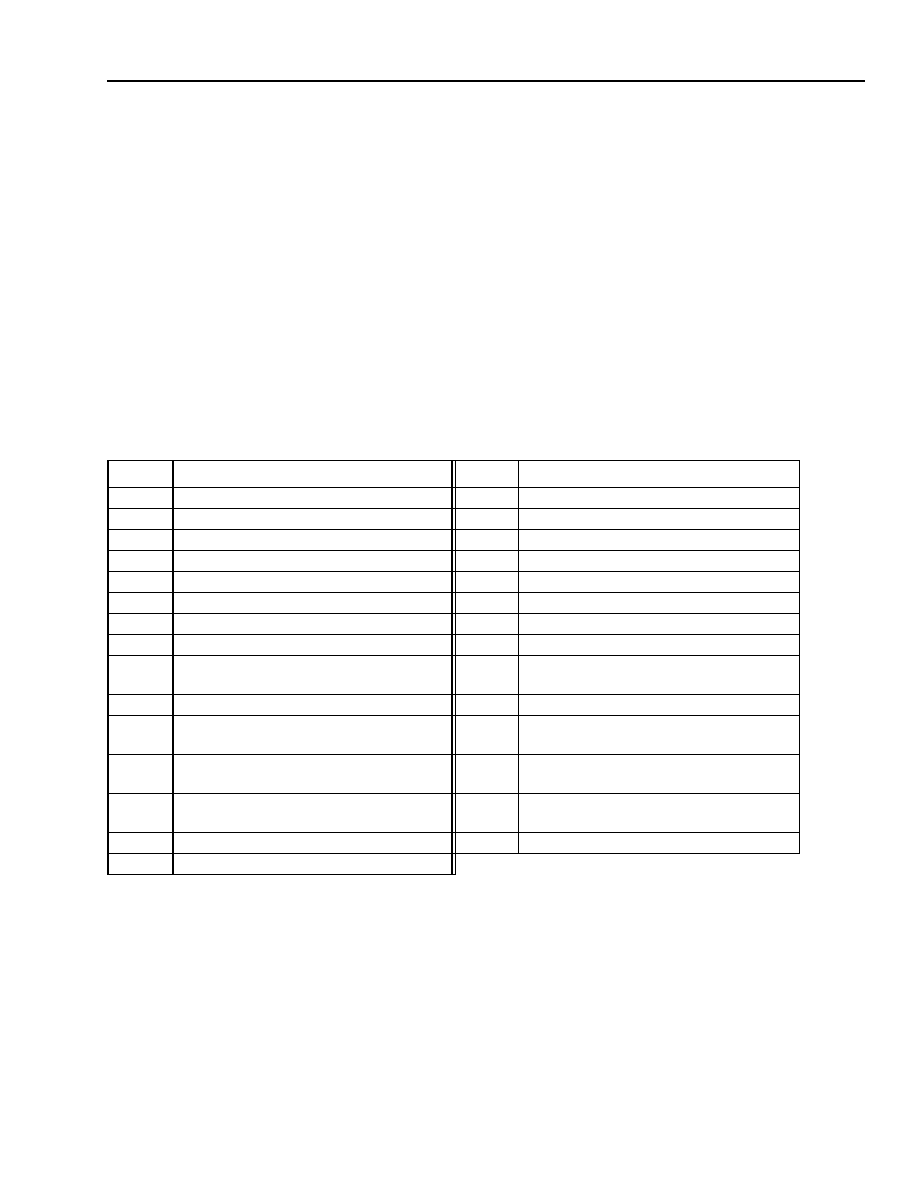

Table 28. B900 Conditional Mnemonics

Test

Meaning

Test

Meaning

pl

Result is nonnegative (sign bit is bit 35).

mi

Result is negative.

eq

Result is equal to 0.

ne

Result is not equal to 0.

gt

Result is greater than 0.

le

Result is less than or equal to 0.

lvs

Logical overflow set.*

* Result is not representable in the 36-bit accumulators (36-bit overflow).

lvc

Logical overflow clear.

mvs

Mathematical overflow set.

Bits 35:31 are not the same (32-bit overflow).

mvc

Mathematical overflow clear.

c0ge

Counter 0 greater than or equal to 0.

c0lt

Counter 0 less than 0.

c1ge

Counter 1 greater than or equal to 0.

c1lt

Counter 1 less than 0.

heads

Pseudorandom sequence bit set.

tails

Pseudorandom sequence bit clear.

true

The condition is always satisfied

in an if instruction.

false

The condition is never satisfied

in an if instruction.

npint

Not PINT (used by JTAG).

njint

Not JINT (used by JTAG).

pllon

B900 core clock is currently phase-

locked loop (CLKPLL).

plloff

B900 core clock is not currently the

phase-locked loop (CLKPLL).

slowon

B900 core clock is currently the low-

frequency clock (CLKLOW).

slowoff

B900 core clock is not currently the low-

frequency clock (CLKLOW).

stopclk STOPCLK is set but the 2X core clock

(CLKCORE2X) has not yet stopped.

evenp

Even parity (from BMU operation).

oddp

Odd parity (from BMU operation).

nmns1

Not minus 1 (result of BMU operation).

mns1

Minus 1 (result of BMU operation).

相关PDF资料 |

PDF描述 |

|---|---|

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

| BA1518SUR5VP | SINGLE COLOR DISPLAY CLUSTER, ULTRA RED |

相关代理商/技术参数 |

参数描述 |

|---|---|

| B-900-M-10 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-10-EG | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20-EG | 制造商:Thomas & Betts 功能描述: |

| B901 | 制造商:EDAL 制造商全称:EDAL 功能描述:Silicon Bridge Rectifier |

发布紧急采购,3分钟左右您将得到回复。