- 您现在的位置:买卖IC网 > PDF目录166397 > B900J24PXX12I 0-BIT, 80 MHz, OTHER DSP, PQFP44 PDF资料下载

参数资料

| 型号: | B900J24PXX12I |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| 文件页数: | 40/100页 |

| 文件大小: | 1547K |

| 代理商: | B900J24PXX12I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

44

Lucent Technologies Inc.

B900

Advance Data Sheet

Baseband Signal Processor

July 1999

5 Software Architecture (continued)

5.1

Instruction Set (continued)

5.1.5 F3 ALU Instructions

These instructions, shown in Table 29, are imple-

mented in the DSP1600 core. F3 ALU instructions

allow accumulator two-operand operations with either

another accumulator, the p register, or a 16-bit immedi-

ate operand. The result is placed in a destination accu-

mulator that can be independently specified. All

operations are done with the full 36 bits. For the accu-

mulator with accumulator operations, both inputs are

36 bits. For the accumulator high with immediate oper-

ations, the immediate is sign-extended into bits 35:32

and the lower bits, 15:0, are filled with zeros, except for

the AND operation, for which they are filled with ones.

These conventions allow the user to do operations with

32-bit immediates by programming two consecutive

16-bit immediate operations.

5.1.6 F4 BMU Instructions

The bit manipulation unit in the B900 provides a set of

efficient bit manipulation operations on accumulators.

It contains four auxiliary registers, ar<0—3> (arM, M =

0, 1, 2, 3), two alternate accumulators (aa0—aa1),

which can be shuffled with the working set, and four

flags (oddp, evenp, mns1, and nms1). The flags are

testable by conditional instructions and can be read

and written via bits 4—7 of the alf register. The BMU

also sets the LMI, LEQ, LLV, and LMV flags in the psw

register:

LMI = 1 if negative (i.e., bit 35 = 1)

LEQ = 1 if zero (i.e., bits 35—0 are 0)

LLV = 1 if (a) 36-bit overflow, or if (b) illegal shift on field

width/offset condition

LMV = 1 if bits 31—35 are not the same (32-bit over-

flow)

The BMU instructions and cycle times follow. All BMU

instructions require 1 word of program memory unless

otherwise noted.

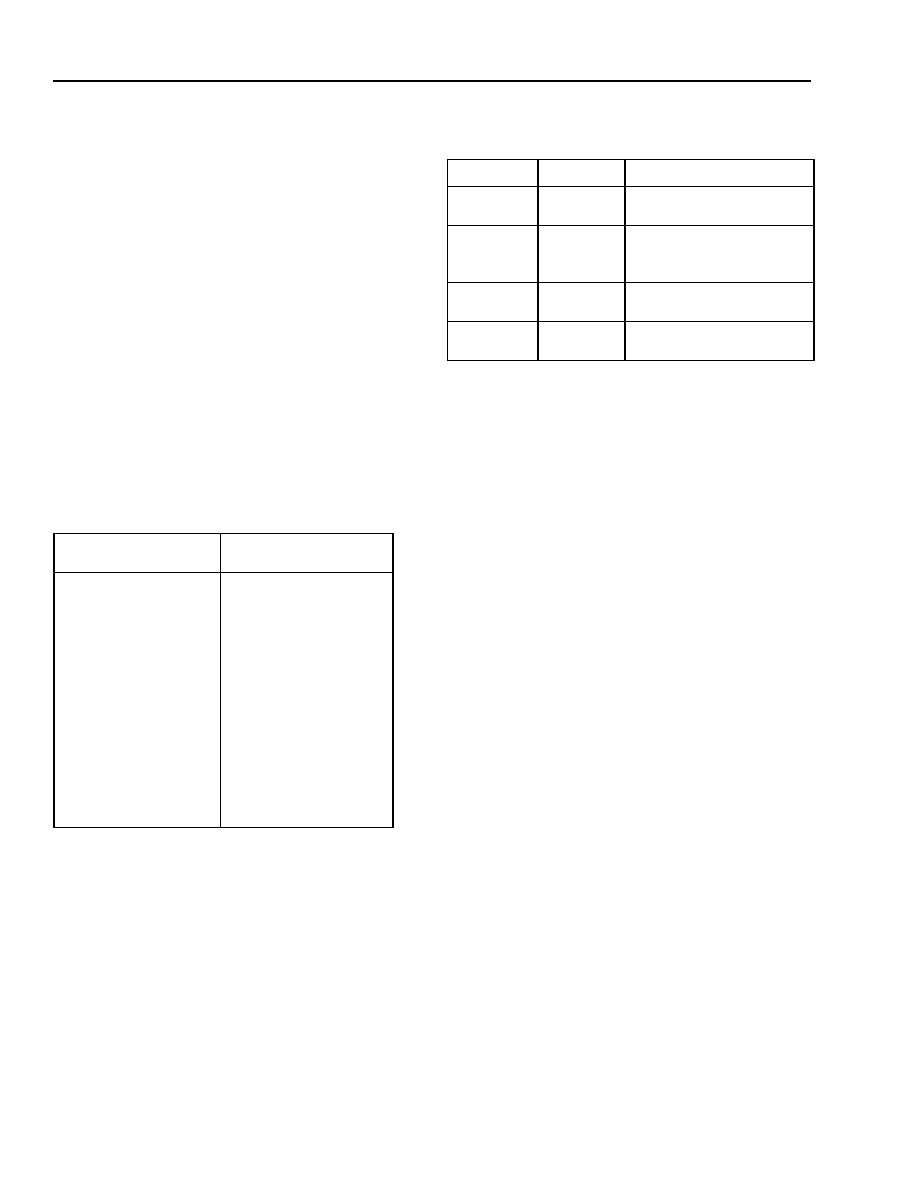

Table 29. F3 ALU Instructions

Cachable

(1 cycle)

Not Cachable

(2 cycle)

aD = aS + aT

aD = aS – aT

aD = aS & aT

aD = aS | aT

aD = aS ^ aT

aS – aT

aS & aT

aD = aS + p

aD = aS – p

aD = aS & p

aD = aS | p

aD = aS ^ p

aS – p

aS & p

aD = aSh + IM16

aD = aSh – IM16

aD = aSh & IM16

aD = aSh | IM16

aD = aSh ^ IM16

aSh – IM16

aSh & IM16

aD = aSl + IM16

aD = aSl – IM16

aD = aSl & IM16

aD = aSl | IM16

aD = aSl ^ IM16

aSl – IM16

aSl & IM16

Table 30. Replacement Table for F3 ALU

Instructions

Replace

Value

Meaning

aD, aT, aS

a0 or a1

One of the two

accumulators.

IM16

16-bit value Long immediate data:

sign-, zero-, or one-

extended as appropriate.

aSh

a0h or a1h Upper half of the

accumulator.

aSl

a0l or a1I

Lower half of the

accumulator.

相关PDF资料 |

PDF描述 |

|---|---|

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

| BA1518SUR5VP | SINGLE COLOR DISPLAY CLUSTER, ULTRA RED |

相关代理商/技术参数 |

参数描述 |

|---|---|

| B-900-M-10 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-10-EG | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20-EG | 制造商:Thomas & Betts 功能描述: |

| B901 | 制造商:EDAL 制造商全称:EDAL 功能描述:Silicon Bridge Rectifier |

发布紧急采购,3分钟左右您将得到回复。