- 您现在的位置:买卖IC网 > PDF目录1924 > IDT82P2828BHG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 28+1CH 640-PBGA PDF资料下载

参数资料

| 型号: | IDT82P2828BHG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 152/154页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 28+1CH 640-PBGA |

| 标准包装: | 5 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 640-BGA 裸露焊盘 |

| 供应商设备封装: | 640-PBGA-EP(31x31) |

| 包装: | 托盘 |

| 其它名称: | 82P2828BHG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页当前第152页第153页第154页

IDT82P2828

28(+1) CHANNEL HIGH-DENSITY T1/E1/J1 LINE INTERFACE UNIT

Programming Information

97

February 6, 2009

RCF1 - Receive Configuration Register 1

Address: 00BH, 04BH, 08BH, 0CBH, 10BH, 14BH, 18BH, 1CBH, (CH1~CH8)

20BH, 24BH, 28BH, 2CBH, 30BH, 34BH, 38BH, 3CBH, (CH9~CH16)

40BH, 44BH, 48BH, 4CBH, 50BH, 54BH, 58BH, 5CBH, (CH17~CH24)

60BH, 64BH, 68BH, 6CBH, (CH25~CH28)

7CBH (CH0)

Type: Read / Write

Default Value: 01H

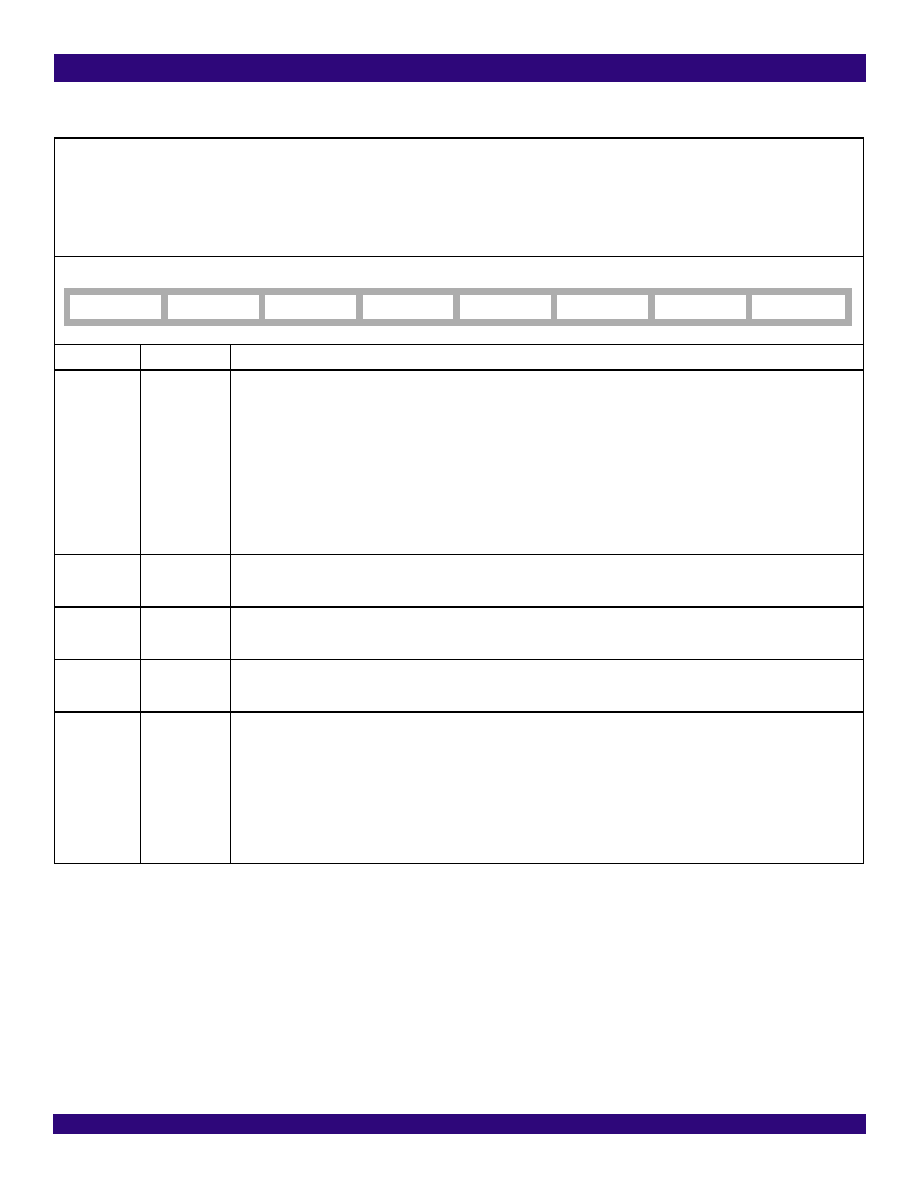

Bit

Name

Description

7 - 5

RMF_DEF[2:0] These bits are valid only in Receive Single Rail NRZ Format mode and Receive Dual Rail Sliced mode. They determine the out-

put on the RMFn pin.

000: PRBS/ARB indication when the PRBS/ARB detection is switched to the receive path. Or reserved when the PRBS/ARB

detection is switched to the transmit path. (default)

001: LAIS indication.

010: XOR data of positive and negative sliced data.

011: Recovered clock (RCLK).

100: LEXZ indication.

101: LBPV indication.

110: LEXZ + LBPV indication.

111: LLOS indication.

4

RCK_ES

This bit selects the active edge of the RCLKn pin.

0: Rising edge. (default)

1: Falling edge.

3

RD_INV

This bit determines the active level on the RDn, RDPn and RDNn pins.

0: Active high. (default)

1: Active low.

2

R_CODE

This bit selects the line code rule for the receive path.

0: B8ZS (in T1/J1 mode) / HDB3 (in E1 mode). (default)

1: AMI.

1 - 0

R_MD[1:0]

These bits determines the receive system interface.

00: Receive Single Rail NRZ Format system interface. The data is output on RDn in NRZ format and a 1.544 MHz (in T1/J1

mode) or 2.048 MHz (in E1 mode) recovered clock is output on RCLKn.

01: Receive Dual Rail NRZ Format system interface. The data is output on RDPn and RDNn in NRZ format and a 1.544 MHz (in

T1/J1 mode) or 2.048 MHz (in E1 mode) recovered clock is output on RCLKn. (default)

10: Receive Dual Rail RZ Format system interface. The data is output on RDPn and RDNn in RZ format and a 1.544 MHz (in T1/

J1 mode) or 2.048 MHz (in E1 mode) recovered clock is output on RCLKn.

11: Receive Dual Rail Sliced system interface. The data is output on RDPn and RDNn in RZ format directly after passing through

the Slicer.

765

432

1

0

RMF_DEF2

RMF_DEF1

RMF_DEF0

RCK_ES

RD_INV

R_CODE

R_MD1

R_MD0

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82P2916BFG | IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088BBG | IC LIU T1/E1/J1 OCTAL 256PBGA |

| IDT82V2041EPPG | IC LIU T1/J1/E1 1CH 44-TQFP |

| IDT82V2042EPFG | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| IDT82V2044EPFG | IC LIU T1/E1 QUAD SHORT 128-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82P2916 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:16-Channel High-Density T1/E1/J1 Line Interface Unit |

| IDT82P2916BFG | 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| IDT82P2916BFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

| IDT82P5088BBBLANK | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

发布紧急采购,3分钟左右您将得到回复。