- 您现在的位置:买卖IC网 > PDF目录1924 > IDT82P2828BHG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 28+1CH 640-PBGA PDF资料下载

参数资料

| 型号: | IDT82P2828BHG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 26/154页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 28+1CH 640-PBGA |

| 标准包装: | 5 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 640-BGA 裸露焊盘 |

| 供应商设备封装: | 640-PBGA-EP(31x31) |

| 包装: | 托盘 |

| 其它名称: | 82P2828BHG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页

IDT82P2828

28(+1) CHANNEL HIGH-DENSITY T1/E1/J1 LINE INTERFACE UNIT

JTAG

121

February 6, 2009

6JTAG

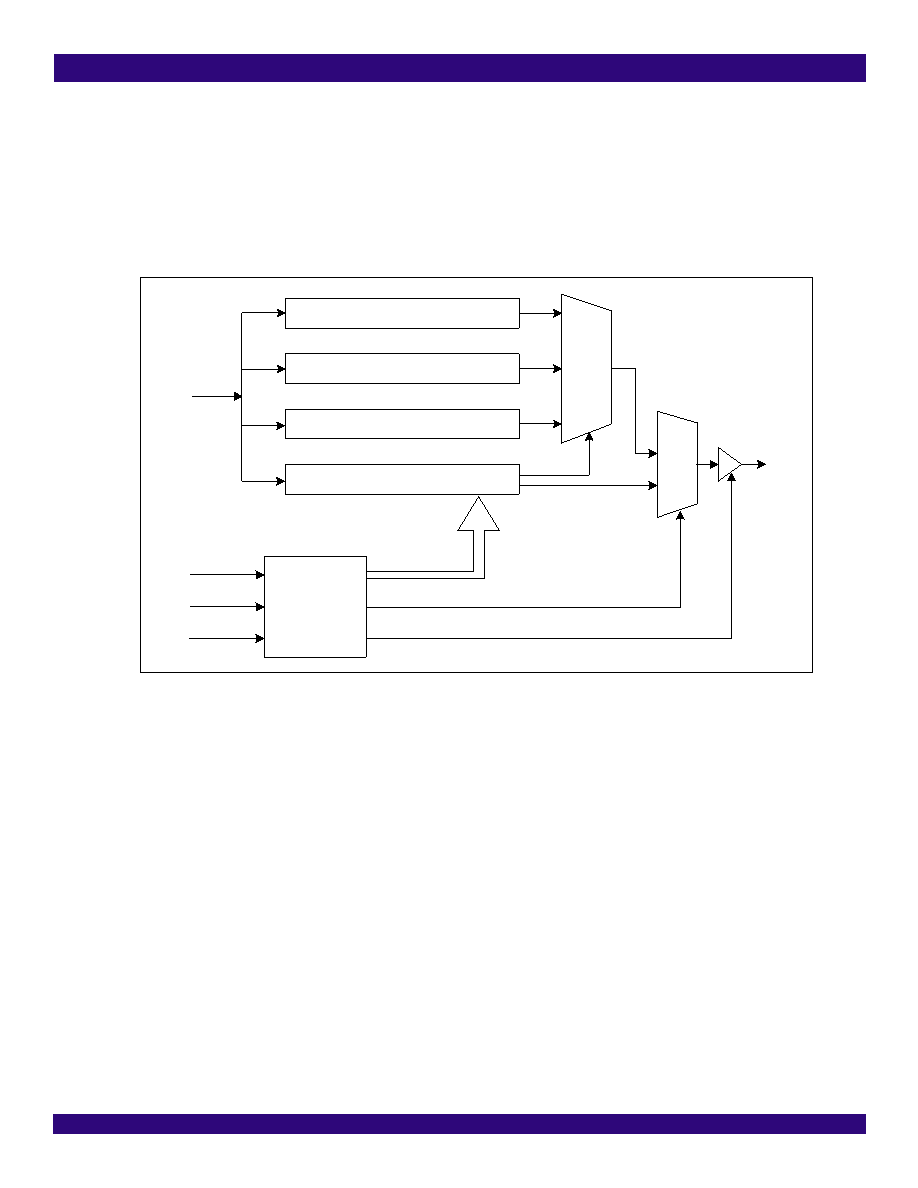

The IDT82P2828 supports the digital Boundary Scan Specification

as described in the IEEE 1149.1 standards.

The boundary scan architecture consists of data and instruction

registers plus a Test Access Port (TAP) controller. The control of the TAP

is achieved through signals applied to the Test Mode Select (TMS) and

Test Clock (TCK) input pins. Data is shifted into the registers via the Test

Data Input (TDI) pin, and shifted out of the registers via the Test Data

Output (TDO) pin. Both TDI and TDO are clocked at a rate determined

by TCK.

The JTAG boundary scan registers include BSR (Boundary Scan

Register), DIR (Device Identification Register), BR (Bypass Register)

and IR (Instruction Register). These will be described in the following

pages. Refer to Figure-50 for architecture.

Figure-50 JTAG Architecture

6.1

JTAG INSTRUCTION REGISTER (IR)

The IR with instruction decode block is used to select the test to be

executed or the data register to be accessed or both.

The instructions include: EXTEST, SAMPLE/PRELOAD, IDCODE,

BYPASS, CLAMP and HIGHZ.

6.2

JTAG DATA REGISTER

6.2.1

DEVICE IDENTIFICATION REGISTER (IDR)

The IDR can be set to define the Version, the Part Number, the

Manufacturer Identity and a fixed bit.

6.2.2

BYPASS REGISTER (BYP)

The BYP consists of a single bit. It can provide a serial path between

the TDI input and the TDO output. Bypassing the BYR will reduce test

access times.

6.2.3

BOUNDARY SCAN REGISTER (BSR)

The bidirectional ports interface to 2 boundary scan cells:

- In cell: The input cell is observable only.

- Out cell: The output cell is controllable and observable.

6.3

TEST ACCESS PORT (TAP) CONTROLLER

The TAP controller is a 16-state synchronous state machine. The

states include: Test Logic Reset, Run-Test/Idle, Select-DR-Scan,

Capture-DR, Shift-DR, Exit1-DR, Pause-DR, Exit2-DR, Update-DR,

Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR, Pause-IR, Exit2-IR and

Update-IR.

Figure-51 shows the state diagram. Note that the figure contains two

main branches to access either the data or instruction registers. The

value shown next to each state transition in this figure states the value

present at TMS at each rising edge of TCK.

BSR (Boundary Scan Register)

DIR (Device Identification Register)

BR (Bypass Register)

IR (Instruction Register)

MUX

TDO

TDI

TCK

TMS

TRST

Control

MUX

Select

Output Enable

TAP

(Test Access

Port) Controller

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82P2916BFG | IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088BBG | IC LIU T1/E1/J1 OCTAL 256PBGA |

| IDT82V2041EPPG | IC LIU T1/J1/E1 1CH 44-TQFP |

| IDT82V2042EPFG | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| IDT82V2044EPFG | IC LIU T1/E1 QUAD SHORT 128-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82P2916 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:16-Channel High-Density T1/E1/J1 Line Interface Unit |

| IDT82P2916BFG | 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| IDT82P2916BFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC LIU T1/E1/J1 16CH SH 484BGA |

| IDT82P5088 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

| IDT82P5088BBBLANK | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Universal Octal T1/E1/J1 LIU with Integrated Clock Adapter |

发布紧急采购,3分钟左右您将得到回复。