- 您现在的位置:买卖IC网 > PDF目录1924 > IDT88P8341BHI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8341BHI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 70/96页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8341BHI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页当前第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

72

IDT88P8341 SPI EXCHANGE SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

SPI-4 egress status register (Block_base 0x0700 +

Register_offset 0x02)

E_CAL_LEN

The E_CAL_LEN value programmed defines the length of

the SPI-4 egress calendar. The actual length of the calendar is four times one

more than the value programmed into the E_CAL_LEN field. For example, if

the E_CAL_LEN field is programmed to 0x3F, the actual value used is 0x100.

The calendar length must be at least as large as the number of active SPI-4

egress LPs.

SPI-4 egress diagnostics register (Block_base

0x0700 + Register_offset 0x05)

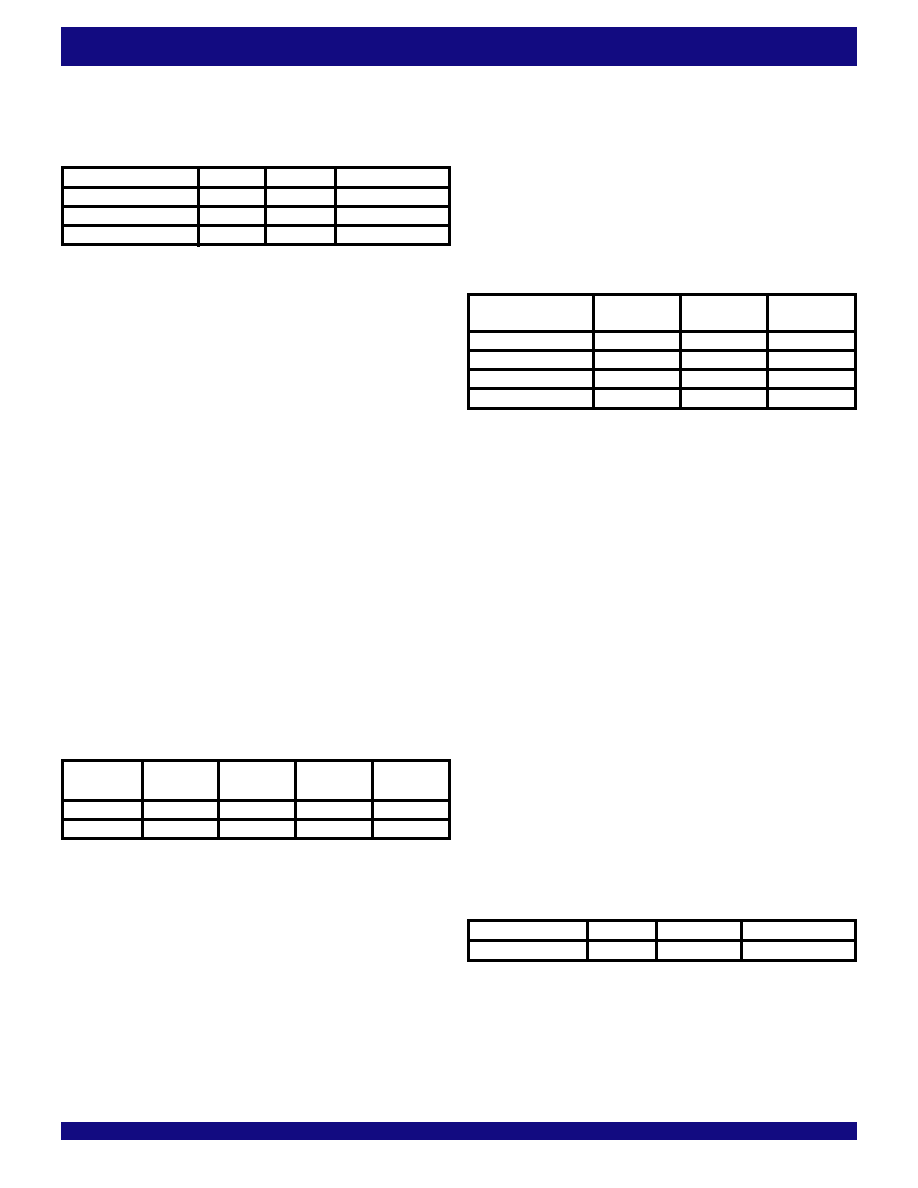

TABLE 106 - SPI-4 EGRESS STATUS REGISTER

(REGISTER_OFFSET 0x02)

Field

Bits

Length

Initial Value

E_SYNCH

0

1

0

E_DSK_OOR

1

0

SCLK_AV

2

1

0

SPI-4 egress status register

TheSPI-4egressstatusregisterisatBlock_base0x0700andhasread-only

access.

The SPI-4 egress status register is used to set the state of the SPI-4 egress

synchronization.

The bit fields of the SPI-4 egress status register are described.

E_SYNCH

The SPI-4 egress E_SYNCH field describes the synchro-

nization state of the SPI-4 egress data path.

0=SPI-4 egress data path is out of synchronization

1=SPI-4 egress data path is in synchronization

E_DSK_OOR

The SPI-4 egress E_DSK_OOR field describes the de-

skew state of the SPI-4 egress data path.

0=SPI-4 egress data path de-skew is within range

1=SPI-4 egress data path de-skew is out of range

SCLK_AV

The SPI-4 egress SCLK_AV field describes the availability

state of the SPI-4 egress status channel clock. This function is not available if

SCLK < 0.5 MCLK.

0=SPI-4 egress status channel clock is not available

1=SPI-4 egress status channel clock is available

SPI-4 egress calendar configuration register

(Block_base 0x0700 + Register_offset 0x03 - 0x04)

TABLE 107 - SPI-4 EGRESS CALENDAR CONFIGU-

RATION REGISTER (REGISTER_OFFSET 0x03 -

0x04)

Field

Acc

Bits

Length

Initial

Value

E_CAL_M

RW

7:0

8

0

E_CAL_LEN

RW

13:8

6

0x01

The SPI-4 egress calendar configuration registers are at Block_base

0x0300 and has read and write access. The Register_offset for calendar_0 is

0x03. The register offset for calendar_1 is 0x04.

The bit fields of the SPI-4 egress calendar configuration register are

described.

The IDT88P8341 calendar length can be programmed to any multiple of 4

using suitable values for the calendar entries, calendar length and calendar

M. If the adjacent device is unable to configure its calendar to be a multiple of

4, conversion logic may be needed between the adjacent device SPI-4

status signals and the 88P8341 signals.

E_CAL_M

The E_CAL_M value programmed defines the number of

timesthecalendarsequenceisrepeatedbeforeaDIP-2parityand“11”framing

words are inserted. The actual calendar_M value used is one more than the

value programmed into the E_CAL_M field.

Field

Bits

Length

Initial

Value

E_FORCE_TRAIN

0

1

0

E_ERR_INS

1

0

E_DIP_NUM

5:2

4

0

BIT_DELAY

7:6

2

0

TheSPI-4egressdiagnosticsregisterisaddressedfromBlock_base0x0700

+ Register_offset 0x05. The SPI-4 egress diagnostics register has read and

writeaccess.

E_FORCE_TRAIN

TheE_FORCE_TRAINfieldisusedtoforcecontinu-

ous training on the SPI-4 egress status interface.

0=Normal status channel operation

1=Force continuous training on the SPI-4 egress status interface

E_ERR_INS The E_ERR_INS field is used to insert the number of DIP-

4 errors on the SPI-4 egress data interface that have been programmed into

theE_DIP_NUMfield.AftertheDIP-4errorsareinserted,theE_ERR_INSfield

willclearitself.

0=Normal status channel operation

1= Insert DIP-4 errors on the SPI-4 egress data interface

E_DIP_NUM The E_DIP_NUM field is used to create DPI-4 errors on the

SPI-4 egress data interface. The number of errors generated is equal to the

value of the E_DIP_NUM field.

BIT_DELAY The BIT_DELAY field is used to delay SPI-4 egress data bit

line 0 by the number of bits programmed into the BIT_DELAY field. This may

be used for diagnostics.

SPI-4 egress DIP-2 error counter (Block_base

0x0700 + Register_offset 0x06)

TABLE 109 - SPI-4 EGRESS DIP-2 ERROR

COUNTER (REGISTER_OFFSET 0x06)

Field

Bits

Length

Initial Value

DIP_2

15:0

16

0

The SPI-4 egress DIP-2 error counter is addressed from Block_base

0x0700+Register_offset0x06.TheSPI-2egressDIP-2errorcounterhasread

access,andautomaticallyclearsitselfafteraread.TheSPI-4egressDIP-2error

counterisusedinportdiagnosticstoverifytheintegrityoftheSPI-4egressstatus

channel.

DIP_2 The DIP_2 field is used to read the number of DIP-2 errors seen on

the SPI-4 egress status interface. The DIP_2 field saturates at the value

TABLE 108 - SPI-4 EGRESS DIAGNOSTICS REGIS-

TER (REGISTER_OFFSET 0x05)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT88P8342BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

| IDT89HPES24NT3ZBBXG | IC PCI SW 24LANE 3PORT 420-SBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。