- 您现在的位置:买卖IC网 > PDF目录4578 > IDT88P8344BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8344BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 68/98页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8344BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

70

IDT88P8344 SPI EXCHANGE 4 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

SPI-4_EN The SPI-4 ingress path is enabled using this field. The SPI-4

pathisdisabledduringresetandwhileconfiguringtheport,andthenisenabled

for normal use.

0=SPI-4 ingress is disabled

1= SPI-4 ingress is enabled

I_CLK_EDGE

The SPI-4 ingress LVTTL status clock active clock edge

is selected using the I_CLK_EDGE field.

0=SPI-4 ingress LVTTL status clock uses the rising edge

1= SPI-4 ingress LVTTL status clock uses the falling edge

I_DSC

The I_DSC bit is used to protect against a random data error

during de-skew.

0= One de-skew result is needed for data de-skew

1= Two consecutive de-skew results are needed for data de-skew

(recommendedsetting)

I_INSYNC_THR

The SPI-4 ingress DIP-4 in synchronization threshold

iscontrolledusingtheI_INSYNC_THRfield.Itisrecommendedtousetheinitial

value.

I_OUTSYNC_THR The SPI-4 ingress DIP-4 out-of synchronization

thresholdiscontrolledusingtheI_OUTSYNC_THRfield.Itisrecommendedto

use the initial value.

I_CSW_EN

The ingress calendar switch enable bit is used to enable the

switching of the active calendars. It is recommended to use the initial value.

0=Ingresscalendarswitchdisabled.OnlySPI-4ingresscalendar_0

is used.

1=Ingress calendar switch enabled. Calendar_0 or calendar_1 can

be used.

CAL_SEL

The calendar select bit selects between SPI-4 ingress

calendar_0 and SPI-4 ingress calendar_1. The CAL_SEL bit is only valid if the

I_CSW_EN bit is set to a logic one.

0=SPI-4 ingress calendar_0 is selected

1=SPI-4ingresscalendar_1isselectediftheI_CSW_ENbitissetto

a logic one

I_LOW

TheI_LOWfieldselectstheSPI-4ingressclockfrequencyrange.

0=SPI-4 ingress clock is greater than or equal to 200 MHz

1=SPI-4 ingress clock is less than 200 MHz

SPI-4 ingress status configuration register

(Block_base 0x0300 + Register_offset 0x01)

FIFO_MAX_T

TheSPI-4ingressFIFO_MAX_Tfieldisthemaximumtime

interval between scheduling of training sequences on the FIFO status path

interface. The units are the number of times the calendar is sent before

scheduling the training sequence.

ALPHA_FIFO

The SPI-4 ingress ALPHA_FIFO field is the number of

repetitions of the status training sequence that must be scheduled every

FIFO_MAX_T cycles. The value for alpha used is actually one more than the

ALPHA_FIFO value programmed into the ALPHA_FIFO field.

SPI-4 ingress status register (Block_base 0x0300 +

Register_offset 0x02)

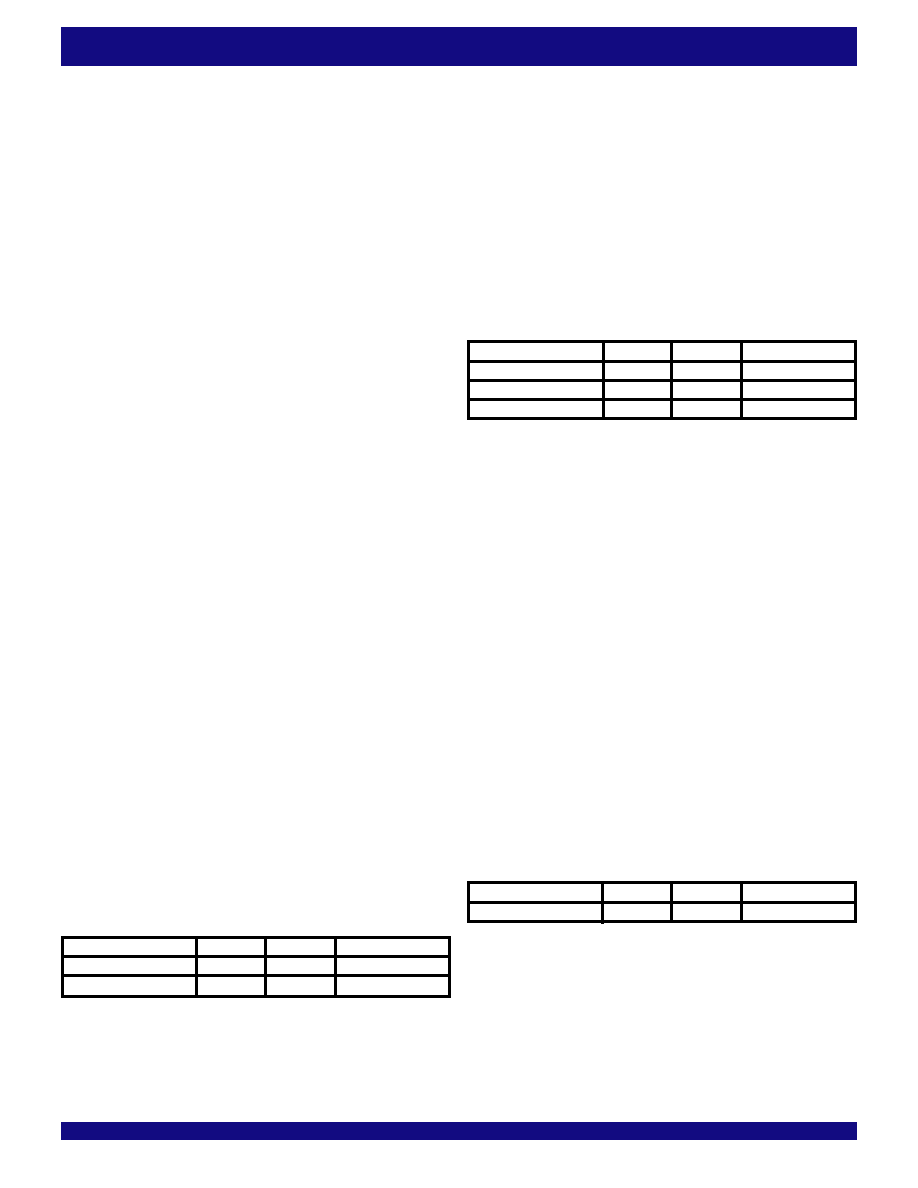

TABLE 90 - SPI-4 INGRESS STATUS CONFIGURA-

TION REGISTER (REGISTER_OFFSET 0x01)

Field

Bits

Length

Initial Value

FIFO_MAX_T

23:0

24

0

ALPHA_FIFO

31:24

8

0

TheSPI-4ingressstatusconfigurationregisterisatBlock_base0x0300and

has read and write access.

The SPI-4 ingress status configuration register is used to set the state of the

SPI-4ingressFIFOstatuspathinterface.ThebitfieldsoftheSPI-4ingressstatus

configuration register are described.

TABLE 91 - SPI-4 INGRESS STATUS REGISTER

(REGISTER_OFFSET 0x02)

Field

Bits

Length

Initial Value

I_SYNCH

0

1

0

I_DSK_OOR

1

0

DCLK_AV

2

1

0

TheSPI-4ingressstatusregisterisatBlock_base0x0300andhasread-only

access.

The SPI-4 ingress status register is used to set the state of the SPI-4 ingress

synchronization.

The bit fields of the SPI-4 ingress status register are described.

I_SYNCH The SPI-4 ingress I_SYNCH field describes the synchroniza-

tion state of the SPI-4 ingress data path.

0=SPI-4 ingress data path is out of synchronization

1=SPI-4 ingress data path is in synchronization

I_DSK_OOR TheSPI-4ingressI_DSK_OORfield describesthede-skew

state of the SPI-4 ingress data path.

0=SPI-4 ingress data path de-skew is within range

1= SPI-4 ingress data path de-skew is out of range

DCLK_AV

The SPI-4 ingress DCLK_AV field describes the availability

state of the SPI-4 ingress clock.

0=SPI-4 ingress clock is not available

1= SPI-4 ingress clock is available

SPI-4 ingress inactive transfer port (Block_base

0x0300 + Register_offset 0x03)

TABLE 92 - SPI-4 INGRESS INACTIVE TRANSFER

PORT (REGISTER_OFFSET 0x03)

Field

Bits

Length

Initial Value

INACT_LP

7:0

8

0

The SPI-4 ingress inactive transfer port is at Block_base 0x0300 and has

read-only access.

The SPI-4 ingress inactive transfer port INACT_LP field is used to monitor

the LP associated with the latest inactive transfer. The INACT_LP field can

change at any time and is used for diagnostics only.

INACT_LP

TheSPI-4ingressINACT_LPfieldcontainsthenumericvalue

oftheLPassociatedwiththelastinactiveLPtransfer,usedfordiagnosticsonly.

相关PDF资料 |

PDF描述 |

|---|---|

| ESM44DRAS | CONN EDGECARD 88POS R/A .156 SLD |

| ASM28DSAS | CONN EDGECARD 56POS R/A .156 SLD |

| ESC60DRTN-S93 | CONN EDGECARD 120PS DIP .100 SLD |

| ESC60DRTH-S93 | CONN EDGECARD 120PS DIP .100 SLD |

| MIC5232-3.3YML TR | IC REG LDO 3.3V 10MA 6-MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBC8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBCG | 功能描述:IC PCI SW 10LANE 4PORT 324BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:PRECISE™ 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBCG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

发布紧急采购,3分钟左右您将得到回复。