- 您现在的位置:买卖IC网 > PDF目录67985 > MCIMX534AVV8C (FREESCALE SEMICONDUCTOR INC) 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 PDF资料下载

参数资料

| 型号: | MCIMX534AVV8C |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 |

| 封装: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, TEPBGA-529 |

| 文件页数: | 126/178页 |

| 文件大小: | 4711K |

| 代理商: | MCIMX534AVV8C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页当前第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页

Electrical Characteristics

i.MX53xA Automotive and Infotainment Applications Processors, Rev. 3

Freescale Semiconductor

51

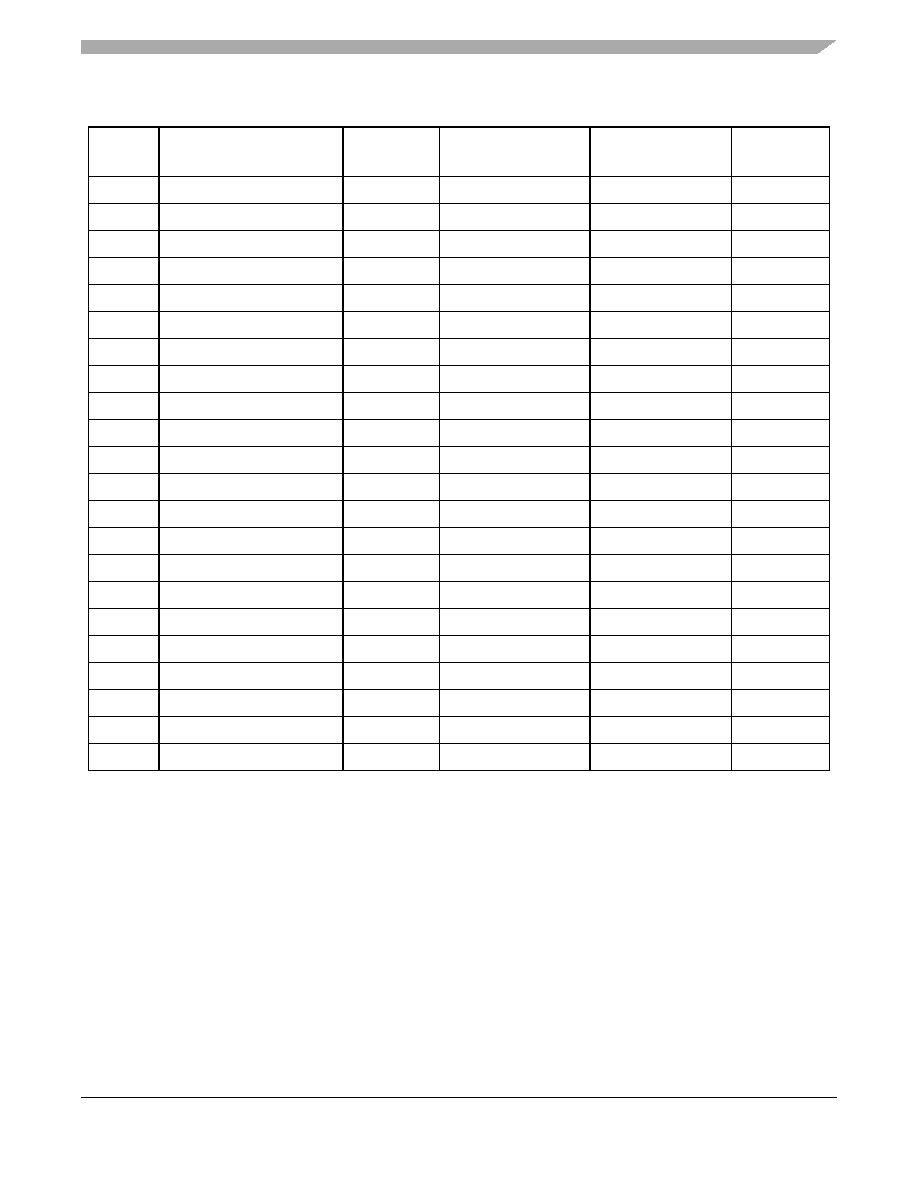

Table 35. NFC—Timing Characteristics

ID

Parameter

Symbol

Asymmetric Mode Min

Symmetric Mode

Min

Max

NF1

NFCLE setup Time

tCLS

2T + 0.1

—

NF2

NFCLE Hold Time

tCLH

T – 4.45

—

NF31

1 In case of NUM_OF_DEVICES is greater than 0 (for example, interleaved mode), then only during the data phase of

symmetric mode the setup time will equal 1.5T + 0.95.

NFCE_B Setup Time

tCS

3T + 0.95

3T+0.95

—

NF4

NFCE_B Hold Time

tCH

2T–5.55

1.5T–5.55

—

NF5

NFWE_B Pulse Width

tWP

T–1.4

0.5T – 1.4

—

NF6

NFALE Setup Time

tALS

2T + 0.1

—

NF7

NFALE Hold Time

tALH

T – 4.45

—

NF8

Data Setup Time

tDS

T–0.9

0.5T – 0.9

—

NF9

Data Hold Time

tDH

T – 5.55

0.5T – 5.55

—

NF10

Write Cycle Time

tWC

2T

T–0.5

—

NF11

NFWE_B Hold Time

tWH

T – 1.15

0.5T – 1.15

—

NF12

Ready to NFRE_B Low

tRR

9T + 8.9

—

NF13

NFRE_B Pulse Width

tRP

1.5T

0.5T–1

—

NF14

READ Cycle Time

tRC

2T

T

—

NF15

NFRE_B High Hold Time

tREH

0.5T – 1.15

—

NF162

2 tDSR is calculated by the following formula:

Asymmetric mode:

tDSR = tREpd + tDpd + 1/

2T – Tdl

2

Symmetric mode:

tDSR = tREpd + tDpd – Tdl2

tREpd + tDpd = 11.2 ns (including clock skew)

where tREpd is RE propogation delay in the chip including I/O pad delay, and tDpd is Data propogation delay from I/O pad to

EXTMC including I/O pad delay.

tDSR can be used to determine tREA max parameter with the following formula: tREA = 1.5T – tDSR.

Data Setup on READ

tDSR

11.2 + 0.5T – Tdl3

3 Tdl is composed of 4 delay-line units each generates an equal delay with min 1.25 ns and max 1 aclk period (Taclk). Default

is 1/4 aclk period for each delay-line unit, so all 4 delay lines together generates a total of 1 aclk period. Taclk is

“emi_slow_clk” of the system, which default value is 7.5 ns (133 MHz).

11.2 – Tdl2

—

NF174

Data Hold on READ

tDHR

0—

2Taclk +T

NF185

Data Hold on READ

tDHR

—Tdl2 –11.2

2Taclk +T

NF19

CLE to RE delay

tCLR

9T

—

NF20

CE to RE delay

tCRE

T–3.45

T+0.3

NF21

WE high to RE low

tWHR

10.5T

—

NF22

WE high to busy

tWB

——

6T

相关PDF资料 |

PDF描述 |

|---|---|

| MCP23008T-E/SO | 8 I/O, PIA-GENERAL PURPOSE, PDSO18 |

| MCP23008-E/ML | 8 I/O, PIA-GENERAL PURPOSE, PQCC20 |

| MCP23S08T-E/ML | 8 I/O, PIA-GENERAL PURPOSE, PQCC20 |

| MCP23S08T-E/SS | 8 I/O, PIA-GENERAL PURPOSE, PDSO20 |

| MCP23008-E/P | 8 I/O, PIA-GENERAL PURPOSE, PDIP18 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCIMX534AVV8C | 制造商:Freescale Semiconductor 功能描述:IC 32-BIT MPU 800 MHZ 529-BGA |

| MCIMX534AVV8CR2 | 功能描述:处理器 - 专门应用 iMX53 Rev 2.1 Auto RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1B | 功能描述:处理器 - 专门应用 IMX53 REV 2.0 COMM RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1C | 功能描述:处理器 - 专门应用 IMX53 REV 2.1 COMM RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1C | 制造商:Freescale Semiconductor 功能描述:IMX53 REV 2.1 COMM |

发布紧急采购,3分钟左右您将得到回复。