- 您现在的位置:买卖IC网 > PDF目录67985 > MCIMX534AVV8C (FREESCALE SEMICONDUCTOR INC) 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 PDF资料下载

参数资料

| 型号: | MCIMX534AVV8C |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 |

| 封装: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, TEPBGA-529 |

| 文件页数: | 172/178页 |

| 文件大小: | 4711K |

| 代理商: | MCIMX534AVV8C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页当前第172页第173页第174页第175页第176页第177页第178页

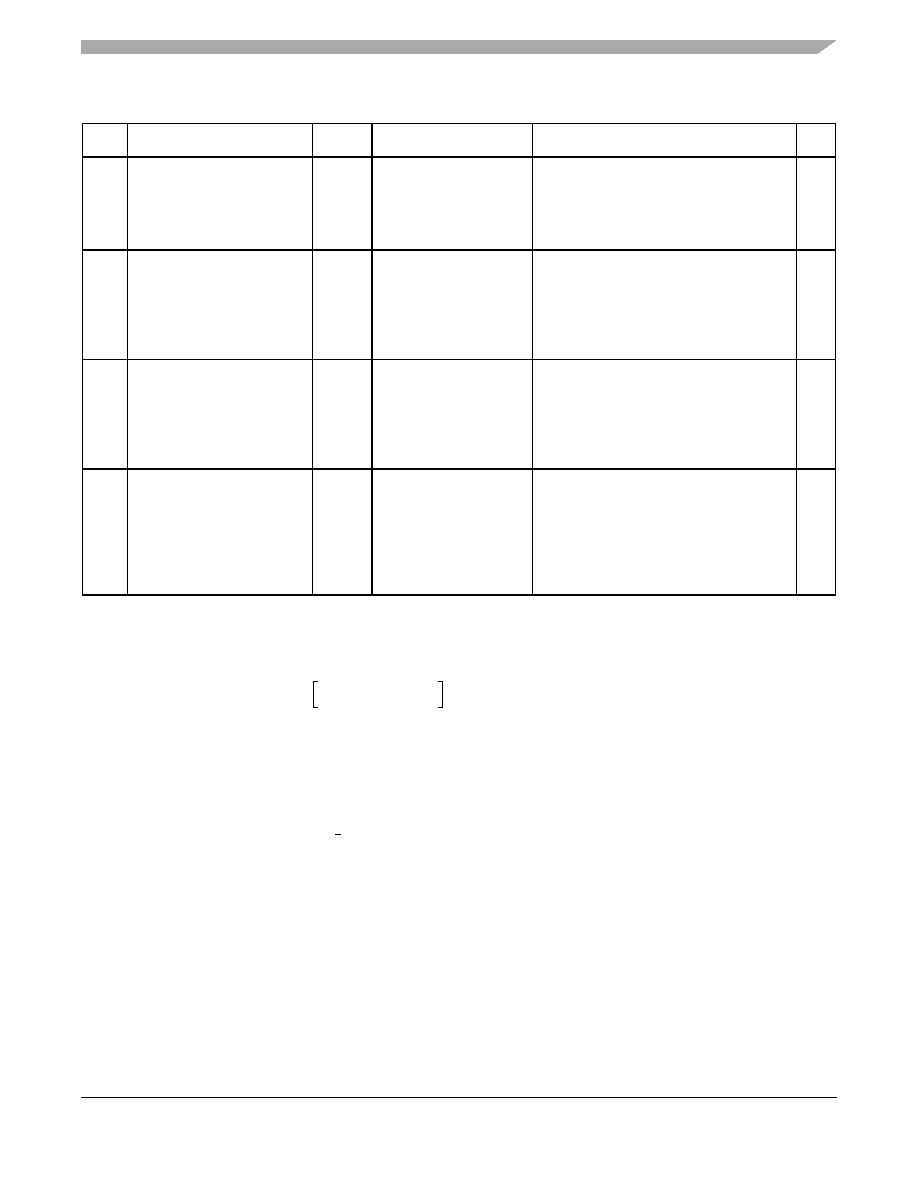

Electrical Characteristics

i.MX53xA Automotive and Infotainment Applications Processors, Rev. 3

Freescale Semiconductor

93

The maximal accuracy of UP/DOWN edge of controls is:

IP5o

Offset of IPP_DISP_CLK

Todicp

DISP_CLK_OFFSET

× Tdiclk

DISP_CLK_OFFSET—offset of

IPP_DISP_CLK edges from local start

point, in DI_CLK

×2

(0.5 DI_CLK Resolution)

Defined by DISP_CLK counter

ns

IP13o Offset of VSYNC

Tovs

VSYNC_OFFSET

× Tdiclk

VSYNC_OFFSET—offset of Vsync edges

from a local start point, when a Vsync

should be active, in DI_CLK

×2

(0.5 DI_CLK Resolution).The

VSYNC_OFFSET should be built by

suitable DI’s counter.

ns

IP8o

Offset of HSYNC

Tohs

HSYNC_OFFSET

× Tdiclk

HSYNC_OFFSET—offset of Hsync edges

from a local start point, when a Hsync

should be active, in DI_CLK

×2

(0.5 DI_CLK Resolution).The

HSYNC_OFFSET should be built by

suitable DI’s counter.

ns

IP9o

Offset of DRDY

Todrdy

DRDY_OFFSET

× Tdiclk

DRDY_OFFSET—offset of DRDY edges

from a suitable local start point, when a

corresponding data has been set on the

bus, in DI_CLK

×2

(0.5 DI_CLK Resolution)

The DRDY_OFFSET should be built by

suitable DI’s counter.

ns

1 Display interface clock period immediate value.

DISP_CLK_PERIOD—number of DI_CLK per one Tdicp. Resolution 1/16 of DI_CLK.

DI_CLK_PERIOD—relation of between programing clock frequency and current system clock frequency

Display interface clock period average value.

2 DI’s counter can define offset, period and UP/DOWN characteristic of output signal according to programed parameters of the

counter. Same of parameters in the table are not defined by DI’s registers directly (by name), but can be generated by

corresponding DI’s counter. The SCREEN_WIDTH is an input value for DI’s HSYNC generation counter. The distance

between HSYNCs is a SCREEN_WIDTH.

Table 60. Synchronous Display Interface Timing Characteristics (Pixel Level) (continued)

ID

Parameter

Symbol

Value

Description

Unit

Tdicp

T

diclk

DISP_CLK_PERIOD

DI_CLK_PERIOD

----------------------------------------------------

×

for integer

DISP_CLK_PERIOD

DI_CLK_PERIOD

----------------------------------------------------

,

T

diclk

floor

DISP_CLK_PERIOD

DI_CLK_PERIOD

----------------------------------------------------

0.5

±

+

for fractional

DISP_CLK_PERIOD

DI_CLK_PERIOD

----------------------------------------------------

,

=

Tdicp

T

diclk

DISP_CLK_PERIOD

DI_CLK_PERIOD

----------------------------------------------------

×

=

Accuracy

0.5

T

diclk

×

() 0.62ns

±

=

相关PDF资料 |

PDF描述 |

|---|---|

| MCP23008T-E/SO | 8 I/O, PIA-GENERAL PURPOSE, PDSO18 |

| MCP23008-E/ML | 8 I/O, PIA-GENERAL PURPOSE, PQCC20 |

| MCP23S08T-E/ML | 8 I/O, PIA-GENERAL PURPOSE, PQCC20 |

| MCP23S08T-E/SS | 8 I/O, PIA-GENERAL PURPOSE, PDSO20 |

| MCP23008-E/P | 8 I/O, PIA-GENERAL PURPOSE, PDIP18 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCIMX534AVV8C | 制造商:Freescale Semiconductor 功能描述:IC 32-BIT MPU 800 MHZ 529-BGA |

| MCIMX534AVV8CR2 | 功能描述:处理器 - 专门应用 iMX53 Rev 2.1 Auto RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1B | 功能描述:处理器 - 专门应用 IMX53 REV 2.0 COMM RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1C | 功能描述:处理器 - 专门应用 IMX53 REV 2.1 COMM RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MCIMX535DVV1C | 制造商:Freescale Semiconductor 功能描述:IMX53 REV 2.1 COMM |

发布紧急采购,3分钟左右您将得到回复。