- 您现在的位置:买卖IC网 > PDF目录98023 > ML60852A (LAPIS SEMICONDUCTOR CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ML60852A |

| 厂商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封装: | PLASTIC, QFP-44 |

| 文件页数: | 4/82页 |

| 文件大小: | 370K |

| 代理商: | ML60852A |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

FEDL60852A-03

1Semiconductor

ML60852A

11/81

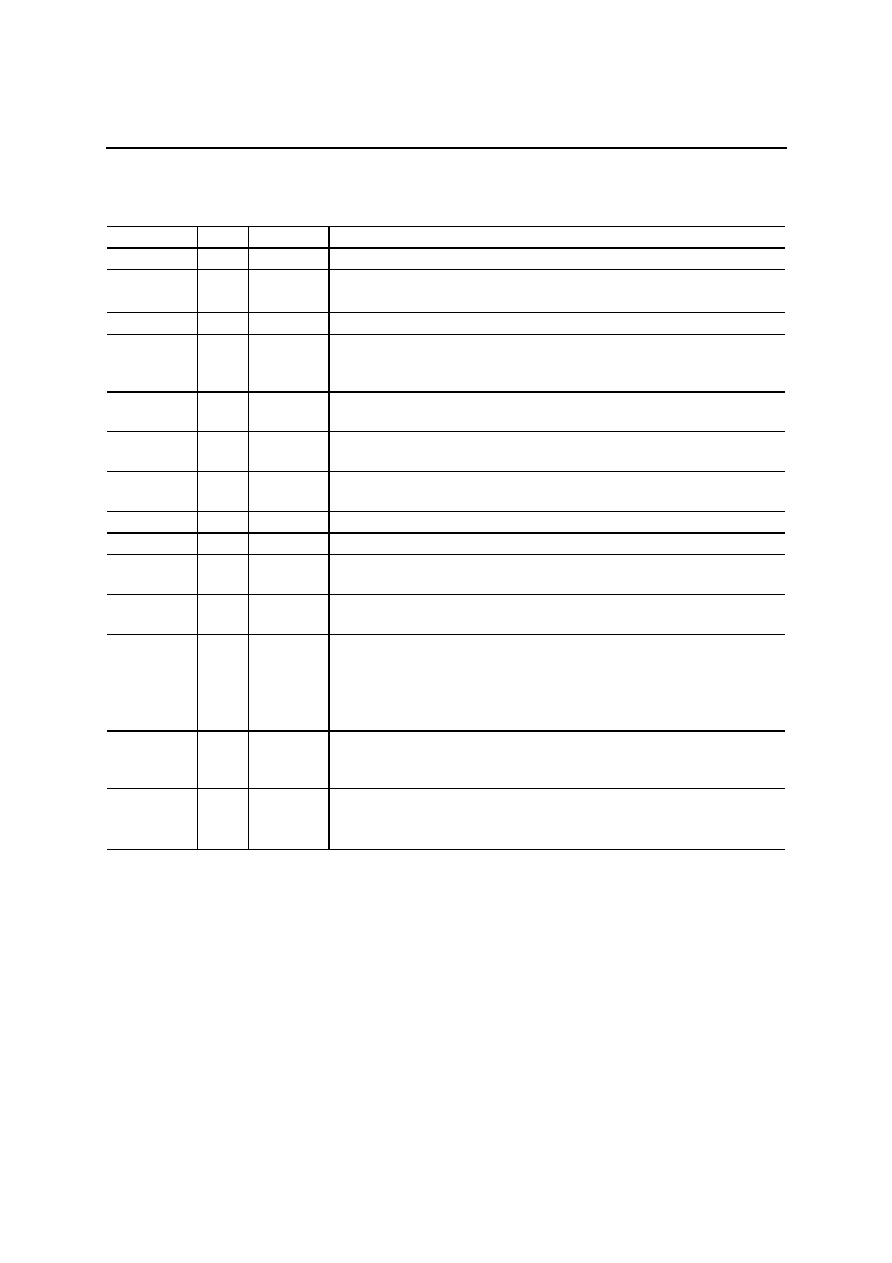

Application Interface

Signal

Type

Assertion

Description

D15: D8

I/O

—

Upper byte (MSB) of data bus.

AD7: AD0

I/O

—

Lower byte (LSB) of data bus when ADSEL is LOW.

Address and lower byte of data bus are multiplexed when ADSEL is HIGH.

A6: A0

I

—

Address when ADSEL is LOW.

CS

ILOW

Chip Select. When this signal is asserted LOW, the ML60852A is selected

and ready to read or write data. This signal is invalid in single address

mode during DMA transfer.

RD

ILOW

Read Strobe. When this signal is asserted LOW, the Read instruction is

executed.

WR

ILOW

Write Strobe. When this signal is asserted LOW, the Write instruction is

executed.

INTR

O

(Note 1)

Interrupt Request. When this signal is asserted, the ML60852A makes an

interrupt request to the application.

DREQ0

O

(Note 1)

DMA Request. This signal requests the DMA0 to make a DMA transfer.

DREQ1

O

(Note 1)

DMA Request. This signal requests the DMA1 to make a DMA transfer.

DACK0

I

(Note 2)

DMA Acknowledge Signal for

DREQ0. This signal, when asserted, enables

accessing FIFOs, without address bus setting.

DACK1

I

(Note 2)

DMA Acknowledge Signal for

DREQ1. This signal, when asserted, enables

accessing FIFO, without address bus setting.

ALE/PUCTL

I or O

HIGH

When ADSEL is HIGH, the address and

CS on AD7: AD0 are latched at the

trailing edge of this signal. D+ pull-up resistor connection output when

ADSEL is LOW.

V

CC potential when bit D3 of SYSCON register is “1”, and high-impedance

when it is “0”.

ADSEL

I

—

When ADSEL is LOW, the address is input on A6: A0 and data is input on

AD7: AD0. When ADSEL is HIGH, address and data are multiplexed on

AD7: AD0.

RESET

ILOW

System Reset. When this signal is asserted LOW, the ML60852A is reset.

When the ML60852A is powered on, this signal must be asserted for 1

s

or more.

Notes: 1. The assertion polarity can be modified by appropriately initializing the polarity selection

register (POLSEL).

The default is LOW.

2. The assertion polarity can be modified by appropriately initializing the polarity selection

register (POLSEL).

The default is HIGH.

相关PDF资料 |

PDF描述 |

|---|---|

| ML63187-XXXGA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP128 |

| ML63193-XXXWA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC128 |

| ML64168-XXX | 4-BIT, MROM, 0.7 MHz, MICROCONTROLLER, UUC80 |

| ML64P168-NGP | 4-BIT, OTPROM, 0.7 MHz, MICROCONTROLLER, PQFP80 |

| ML64P168-NGA | 4-BIT, OTPROM, 0.7 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ML60852ATBZ010 | 功能描述:USB 接口集成电路 12 Mbps; USB Device Controller RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| ML60852ATBZ03A | 制造商:ROHM Semiconductor 功能描述: |

| ML-60-V2/80721 | 制造商:Thomas & Betts 功能描述: |

| ML61 | 制造商:MINILOGIC 制造商全称:MINILOGIC 功能描述:Series Positive Voltage Detector |

| ML61_09 | 制造商:MINILOGIC 制造商全称:MINILOGIC 功能描述:Positive Voltage Detector CMOS Low Power Consumption : Typical 1.0uA at Vin=2.0V |

发布紧急采购,3分钟左右您将得到回复。