- 您现在的位置:买卖IC网 > PDF目录18758 > SX1211I084TRT (Semtech)IC SNGL-CHIP TXRX 32-TQFN PDF资料下载

参数资料

| 型号: | SX1211I084TRT |

| 厂商: | Semtech |

| 文件页数: | 40/92页 |

| 文件大小: | 0K |

| 描述: | IC SNGL-CHIP TXRX 32-TQFN |

| 标准包装: | 1 |

| 频率: | 860 ~ 960MHz |

| 数据传输率 - 最大: | 200kbps |

| 调制或协议: | FSK,OOK |

| 应用: | AMR,ISM,安防门禁 |

| 功率 - 输出: | 12.5dBm |

| 灵敏度: | -113dBm |

| 电源电压: | 2.1 V ~ 3.6 V |

| 电流 - 接收: | 3mA |

| 电流 - 传输: | 25mA |

| 数据接口: | PCB,表面贴装 |

| 天线连接器: | PCB,表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 32-TQFN |

| 包装: | 标准包装 |

| 产品目录页面: | 584 (CN2011-ZH PDF) |

| 配用: | 1210-1060-2-ND - 915MHZ ASPICS SX1211 CHIP SET 1210-1059-2-ND - 868MHZ ASPICS SX1211 CHIP SET 1210-1060-6-ND - 915MHZ ASPICS SX1211 CHIP SET 1210-1059-6-ND - 868MHZ ASPICS SX1211 CHIP SET 1210-1060-1-ND - 915MHZ ASPICS SX1211 CHIP SET 1210-1059-1-ND - 868MHZ ASPICS SX1211 CHIP SET |

| 其它名称: | SX1211I084DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

�� �

�

�

�SX1211�

�WIRELESS� &� SENSING�

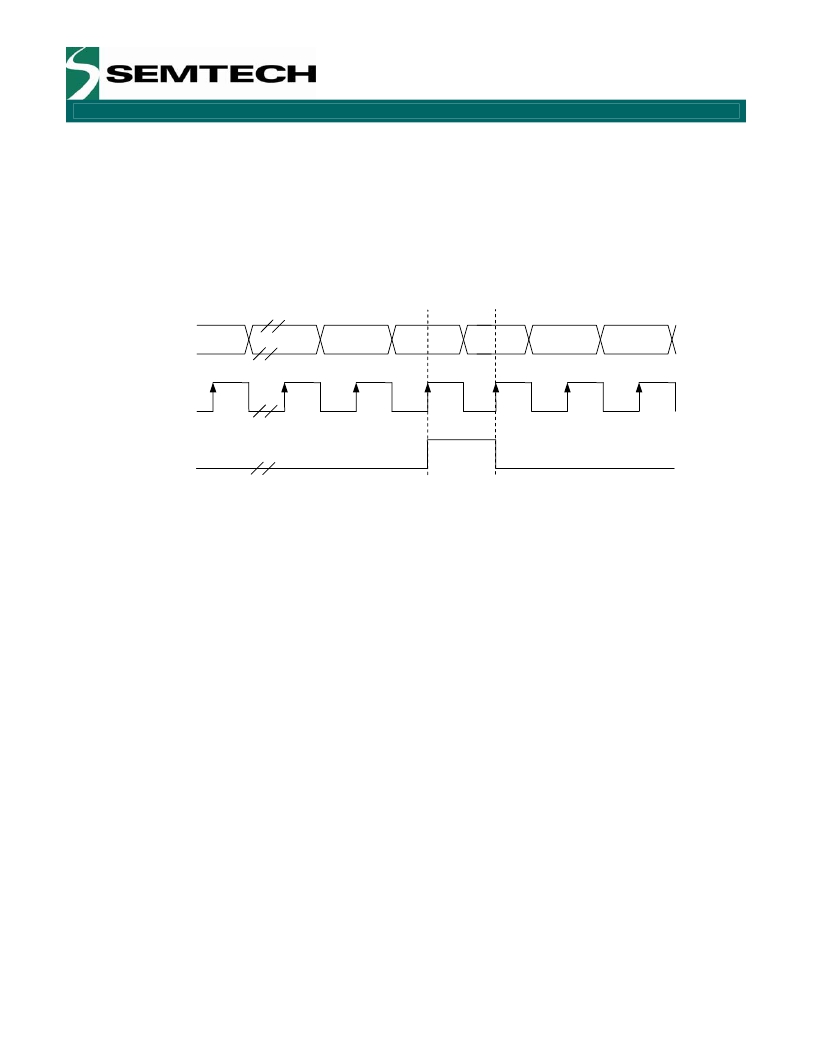

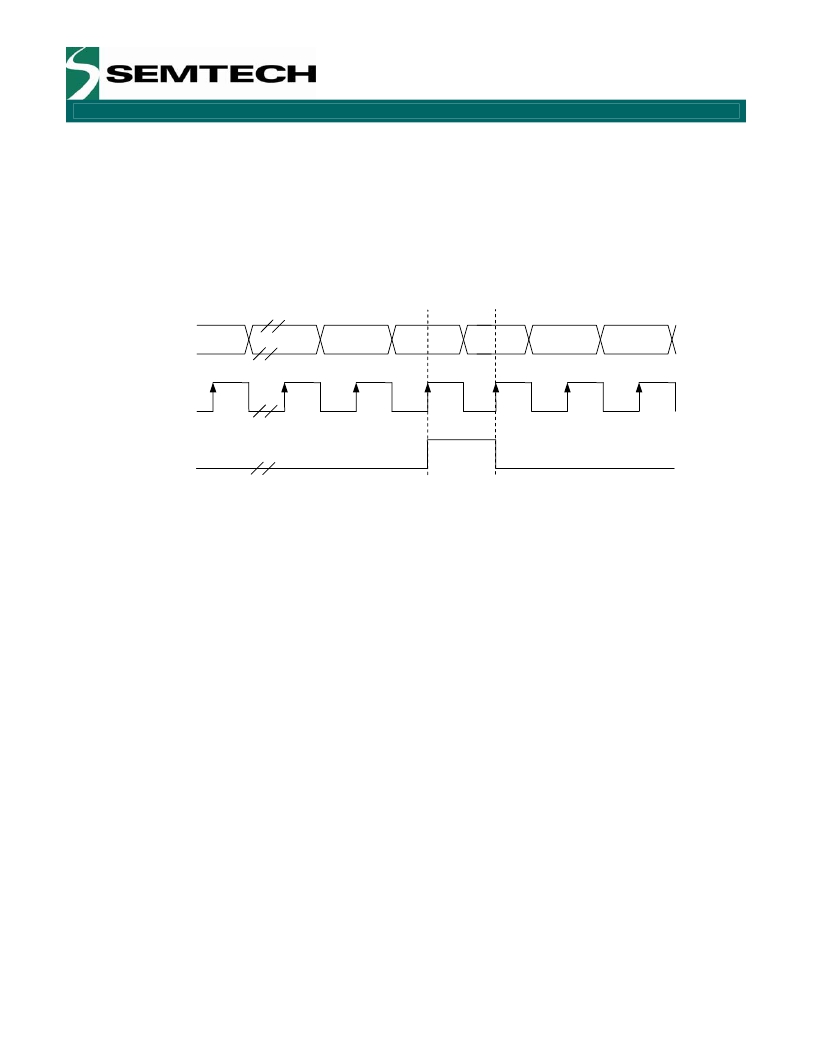

�5.2.3.� Sync� Word� Recognition�

�5.2.3.1.� Overview�

�Sync� word� recognition� (also� called� Pattern� recognition� in� previous� products)� is� activated� by� setting�

�RXParam_Sync_on.� The� bit� synchronizer� must� also� be� activated.�

�The� block� behaves� like� a� shift� register;� it� continuously� compares� the� incoming� data� with� its� internally� programmed�

�Sync� word� and� asserts� the� Sync� IRQ� source� on� each� occasion� that� a� match� is� detected.� This� is� illustrated� in� Figure�

�33.�

�Rx� DATA�

�(NRZ)�

�Bit� N-x� =�

�Sync_value[x]�

�Bit� N-1� =� Bit� N� =�

�Sync_value[1]� Sync_value[0]�

�DCLK�

�SYNC�

�Figure� 33:� Sync� Word� Recognition�

�During� the� comparison� of� the� demodulated� data,� the� first� bit� received� is� compared� with� bit� 7� (MSB)� of� byte� at�

�address� 22� and� the� last� bit� received� is� compared� with� bit� 0� (LSB)� of� the� last� byte� whose� address� is� determined� by�

�the� length� of� the� Sync� word.�

�When� the� programmed� Sync� word� is� detected� the� user� can� assume� that� this� incoming� packet� is� for� the� node� and�

�can� be� processed� accordingly.�

�5.2.3.2.� Configuration�

�Size:� Sync� word� size� can� be� set� to� 8,� 16,� 24� or� 32� bits� via� RXParam_Sync_size.� In� Packet� mode� this� field� is�

�also� used� for� Sync� word� generation� in� Tx� mode.�

�Error� tolerance:� The� number� of� errors� tolerated� in� the� Sync� word� recognition� can� be� set� to� 0,� 1,� 2� or� 3� via�

�RXParam_Sync_tol.�

�Value:� The� Sync� word� value� is� configured� in� SYNCParam_Sync_value.� In� Packet� mode� this� field� is� also� used�

�for� Sync� word� generation� in� Tx� mode.�

�5.2.4.� Packet� Handler�

�The� packet� handler� is� the� block� used� in� Packet� mode.� Its� functionality� is� fully� described� in� section� 5.5.�

�5.2.5.� Control�

�The� control� block� configures� and� controls� the� full� chip’s� behavior� according� to� the� settings� programmed� in� the�

�configuration� registers.�

�Rev� 8� –� February� 2013�

�Page� 40� of� 92�

�www.semtech.com�

�相关PDF资料 |

PDF描述 |

|---|---|

| 12-900-LPI | XFRMR PWR 115/230V 12.6VCT 900MA |

| 10-1200-LPI | XFRMR PWR 115/230V 10VCT 1.2A |

| MT-6-12 | XFRMR 115V 5V 1.75A 6VA 3OUT |

| ATMEGA64RZAV-10MU | MCU ATMEGA644/AT86RF230 44-QFN |

| ATMEGA128RFA1-ZU | IC AVR MCU 2.4GHZ XCEIVER 64QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SX1211I084TRT | 制造商:Semtech Corporation 功能描述:GPSS WL SKU APP1 |

| SX1211I084TRT-CUT | 制造商:Semtech Corporation 功能描述: |

| SX1211I097.TRT | 制造商:Semtech Corporation 功能描述: |

| SX1211MESH-868 | 制造商:Semtech Corporation 功能描述:10 MODULES MESH NETWORK |

| SX1211SK868 | 制造商:Semtech Corporation 功能描述:Full Evalulation Kit For Ultra-Low Power Integrated UHF Transceiver |

发布紧急采购,3分钟左右您将得到回复。