- 您现在的位置:买卖IC网 > PDF目录19483 > ADSP-21375KSWZ-2B (Analog Devices Inc)IC DSP 32BIT 266MHZ 208-MQFP PDF资料下载

参数资料

| 型号: | ADSP-21375KSWZ-2B |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/56页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 266MHZ 208-MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 36 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 266MHz |

| 非易失内存: | ROM(256 kB) |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LQFP 裸露焊盘 |

| 供应商设备封装: | 208-LQFP-EP(28x28) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

�� �

�

�

�ADSP-21371� /� ADSP-21375�

�DMA� channels,� one� for� transmit� and� one� for� receive.� These�

�DMA� channels� have� lower� default� priority� than� most� DMA�

�channels� because� of� their� relatively� low� service� rates.�

�port� (PDAP),� or� the� UART� (see� Table� 7� ).�

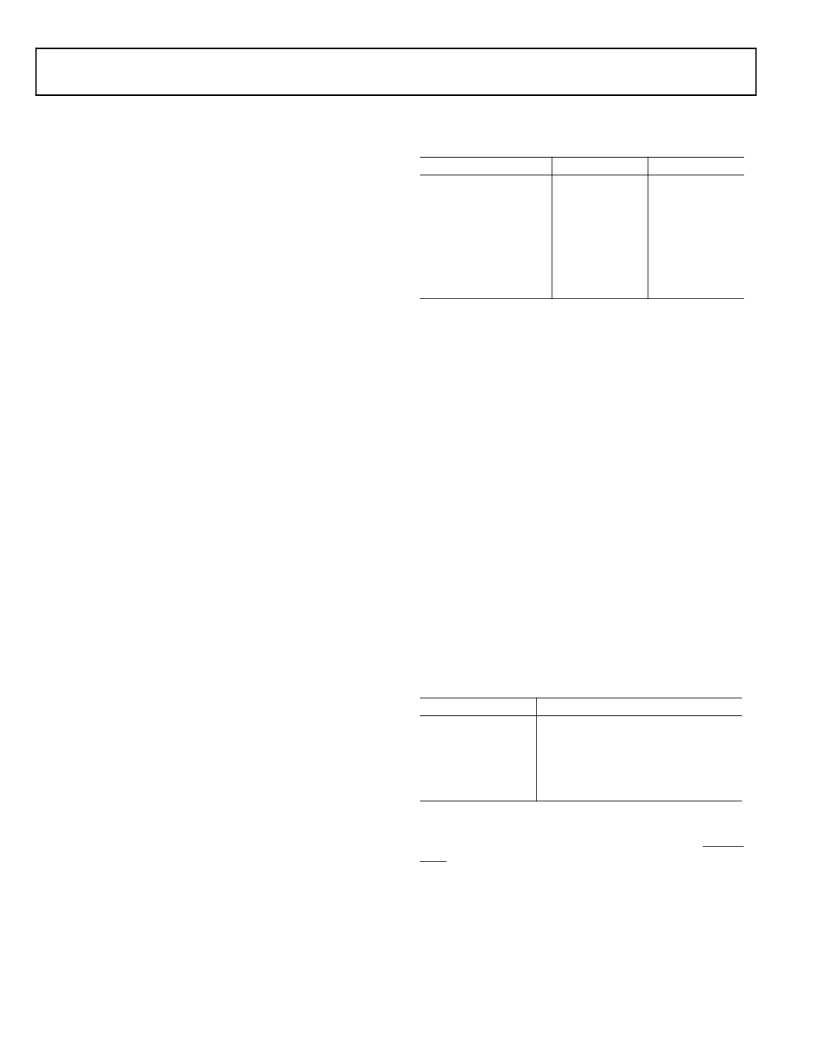

�Table� 7.� DMA� Channels�

�The� UART� port’s� baud� rate,� serial� data� format,� error� code� gen-�

�eration� and� status,� and� interrupts� are� programmable.� The� port:�

�?� Supports� bit� rates� ranging� from� (f� PCLK� /1,048,576)� to�

�(f� PCLK� /16)� bits� per� second.�

�?� Supports� data� formats� from� 7� to� 12� bits� per� frame.�

�?� Can� be� configured� to� generate� maskable� interrupts� for� both�

�transmit� and� receive� operations.�

�In� conjunction� with� the� general-purpose� timer� functions,� auto-�

�baud� detection� is� supported.�

�Peripheral�

�SPORT�

�PDAP�

�SPI�

�UART�

�EP�

�MTM/DTCP�

�Total� DMA� Channels�

�ADSP-21371�

�16�

�8�

�2�

�2�

�2�

�2�

�32�

�ADSP-21375�

�8�

�8�

�2�

�2�

�2�

�2�

�24�

�Peripheral� Timers�

�Two� general-purpose� timers� can� generate� periodic� interrupts�

�and� be� independently� set� to� operate� in� one� of� three� modes:�

�?� Pulse� waveform� generation� mode�

�?� Pulse� width� count/capture� mode�

�?� External� event� watchdog� mode�

�Each� general-purpose� timer� has� one� bidirectional� pin� and� four�

�registers� that� implement� its� mode� of� operation:� a� 6-bit� configu-�

�ration� register,� a� 32-bit� count� register,� a� 32-bit� period� register,�

�and� a� 32-bit� pulse� width� register.� A� single� control� and� status�

�register� enables� or� disables� the� general-purpose� timers�

�independently.�

�2-Wire� Interface� Port� (TWI)�

�The� TWI� is� a� bidirectional� 2-wire� serial� bus� used� to� move� 8-bit�

�data� while� maintaining� compliance� with� the� I� 2� C� bus� protocol.�

�The� TWI� master� incorporates� the� following� features:�

�?� Simultaneous� master� and� slave� operation� on� multiple�

�device� systems� with� support� for� multi� master� data�

�arbitration�

�?� Digital� filtering� and� timed� event� processing�

�?� 7-bit� addressing�

�?� 100� kbps� and� 400� kbps� data� rates�

�Delay� Line� DMA�

�The� processors� provide� delay� line� DMA� functionality.� This�

�allows� processor� reads� and� writes� to� external� delay� line� buffers�

�(and� hence� to� external� memory)� with� limited� core� interaction.�

�Scatter/Gather� DMA�

�The� ADSP-2137x� processor� provides� scatter/gather� DMA� func-�

�tionality.� This� allows� processor� DMA� reads/writes� to/from� non-�

�contiguous� memory� blocks.�

�SYSTEM� DESIGN�

�The� following� sections� provide� an� introduction� to� system� design�

�options� and� power� supply� issues.� For� complete� system� design�

�information,� see� the� ADSP-2137x� SHARC� Processor� Hardware�

�Reference� .�

�Program� Booting�

�The� internal� memory� of� the� processor� boots� at� system� power-up�

�from� an� 8-bit� EPROM� via� the� external� port,� an� SPI� master,� or� an�

�SPI� slave.� Booting� is� determined� by� the� boot� configuration�

�(BOOT_CFG1–0)� pins� in� Table� 8� .� Selection� of� the� boot� source�

�is� controlled� via� the� SPI� as� either� a� master� or� slave� device,� or� it�

�can� immediately� begin� executing� from� ROM.�

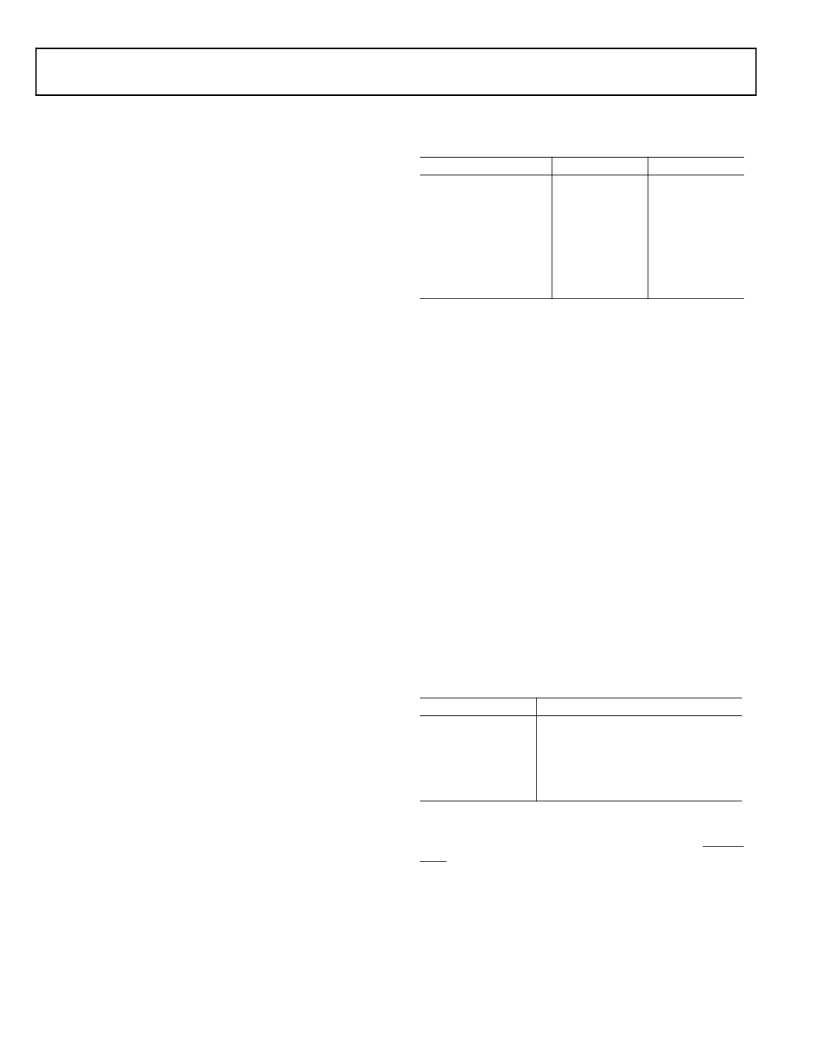

�Table� 8.� Boot� Mode� Selection�

�?� Low� interrupt� rate�

�I/O� PROCESSOR� FEATURES�

�The� I/O� processor� provides� many� channels� of� DMA� and� con-�

�trols� the� extensive� set� of� peripherals� described� in� the� previous�

�BOOT_CFG1–0�

�00�

�01�

�10�

�11�

�Booting� Mode�

�SPI� Slave� Boot�

�SPI� Master� Boot�

�EPROM/FLASH� Boot�

�No� boot� (processor� executes� from�

�sections.�

�DMA� Controller�

�The� processor’s� on-chip� DMA� controller� allows� data� transfers�

�without� processor� intervention.� The� DMA� controller� operates�

�independently� and� invisibly� to� the� processor� core,� allowing�

�internal� ROM� after� reset)�

�The� “Running� Reset”� feature� allows� programs� to� perform� a� reset�

�of� the� processor� core� and� peripherals,� but� without� resetting� the�

�PLL� and� SDRAM� controller,� or� performing� a� boot.� The� RESET-�

�OUT� pin� acts� as� the� input� for� initiating� a� running� reset.�

�DMA� operations� to� occur� while� the� core� is� simultaneously� exe-�

�cuting� its� program� instructions.� DMA� transfers� can� occur�

�between� the� ADSP-2137x� processor’s� internal� memory� and� its�

�serial� ports,� the� SPI-compatible� (serial� peripheral� interface)�

�ports,� the� IDP� (input� data� port),� the� parallel� data� acquisition�

�Rev.� D� |� Page� 10� of� 56� |� April� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| SMK316B7682KF-T | CAP CER 6800PF 630V 10% X7R 1206 |

| ECC22DCAH | CONN EDGECARD 44POS R/A .100 SLD |

| XC95144XL-5TQ100C | IC CPLD 144 MCELL 3.3V 100-TQFP |

| VE-20F-CY-F2 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21375KSWZ-2B2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

| ADSP-21375KSWZ-2BX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21375KSZ-2B | 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT/40-BIT 266MHZ 266MIPS 208MQFP - Trays |

| ADSP-21375KSZ-2BX | 制造商:Analog Devices 功能描述:266 MHZ.PROC W/ON CHIPROM,S/PDIF PBFREE - Trays |

| ADSP-21375KSZ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

发布紧急采购,3分钟左右您将得到回复。