- 您现在的位置:买卖IC网 > PDF目录19483 > ADSP-21375KSWZ-2B (Analog Devices Inc)IC DSP 32BIT 266MHZ 208-MQFP PDF资料下载

参数资料

| 型号: | ADSP-21375KSWZ-2B |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/56页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 266MHZ 208-MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 36 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 266MHz |

| 非易失内存: | ROM(256 kB) |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LQFP 裸露焊盘 |

| 供应商设备封装: | 208-LQFP-EP(28x28) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

�� �

�

�

�ADSP-21371� /� ADSP-21375�

�Table� 30.� Serial� Ports—External� Late� Frame� Sync�

�1.0� V,� 200� MHz�

�1.2� V,� 266� MHz�

�Parameter� Min�

�Max�

�Min�

�Max�

�Unit�

�Switching� Characteristics�

�t� DDTLFSE� 1�

�Data� Delay� from� Late� External� Transmit� Frame� Sync�

�12.7�

�10�

�ns�

�or� External� Receive� Frame� Sync� with�

�MCE� =� 1,� MFD� =� 0�

�t� DDTENFS� 1�

�Data� Enable� for� MCE� =� 1,� MFD� =� 0� 0.5�

�0.5�

�ns�

�1�

�The� t� DDTLFSE� and� t� DDTENFS� parameters� apply� to� left-justified� sample� pair� as� well� as� DSP� serial� mode,� and� MCE� =� 1,� MFD� =� 0.�

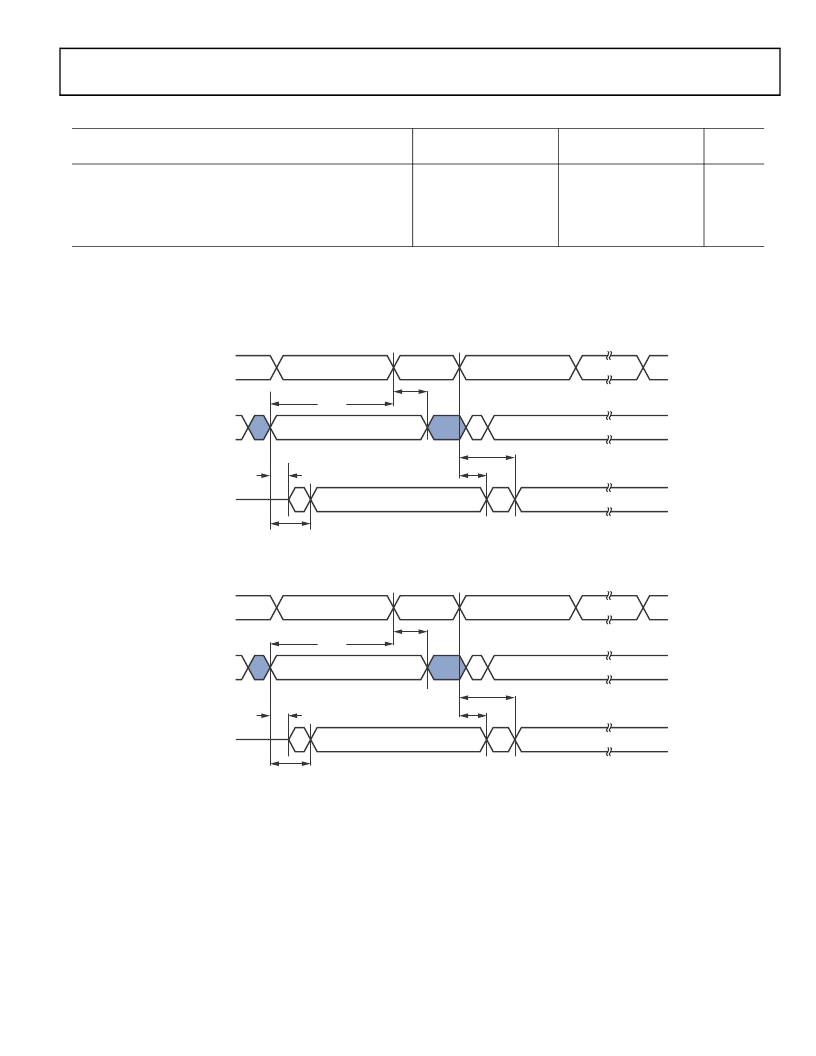

�EXTERNAL� RECEIVE� FS� WITH� MCE� =� 1,� MFD� =� 0�

�DAI_P20–1�

�(SCLK)�

�DAI_P20–1�

�(FS)�

�DRIVE�

�t� SFSE/I�

�SAMPLE�

�t� HFSE/I�

�DRIVE�

�DAI_P20–1�

�(DATA� CHANNEL�

�A/B)�

�t� DDTENFS�

�1ST� BIT�

�t� HDTE/I�

�t� DDTE/I�

�2ND� BIT�

�t� DDTLFSE�

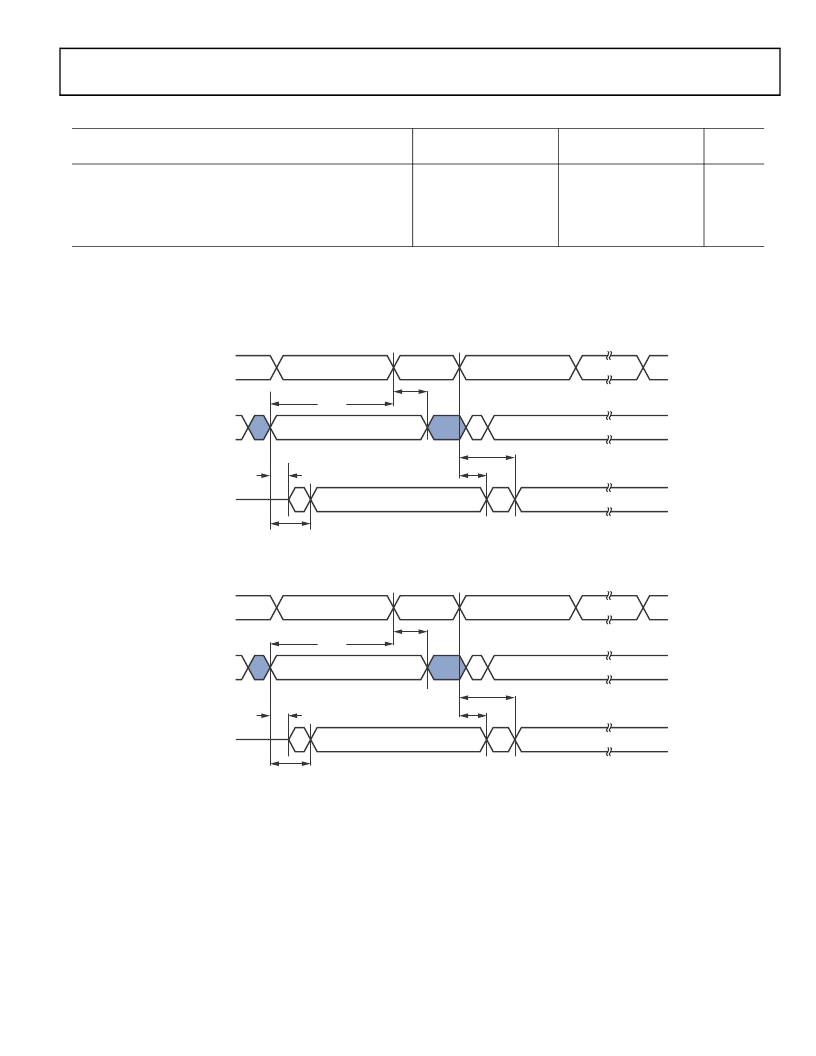

�LATE� EXTERNAL� TRANSMIT� FS�

�DAI_P20–1�

�(SCLK)�

�DAI_P20–1�

�(FS)�

�DRIVE�

�t� SFSE/I�

�SAMPLE�

�t� HFSE/I�

�DRIVE�

�DAI_P20–1�

�(DATA� CHANNEL�

�A/B)�

�t� DDTENFS�

�1ST� BIT�

�t� HDTE/I�

�t� DDTE/I�

�2ND� BIT�

�t� DDTLFSE�

�Figure� 22.� External� Late� Frame� Sync� 1�

�1�

�This� figure� reflects� changes� made� to� support� left-justified� sample� pair� mode.�

�Rev.� D� |� Page� 37� of� 56� |� April� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| SMK316B7682KF-T | CAP CER 6800PF 630V 10% X7R 1206 |

| ECC22DCAH | CONN EDGECARD 44POS R/A .100 SLD |

| XC95144XL-5TQ100C | IC CPLD 144 MCELL 3.3V 100-TQFP |

| VE-20F-CY-F2 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21375KSWZ-2B2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

| ADSP-21375KSWZ-2BX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21375KSZ-2B | 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT/40-BIT 266MHZ 266MIPS 208MQFP - Trays |

| ADSP-21375KSZ-2BX | 制造商:Analog Devices 功能描述:266 MHZ.PROC W/ON CHIPROM,S/PDIF PBFREE - Trays |

| ADSP-21375KSZ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

发布紧急采购,3分钟左右您将得到回复。