- 您现在的位置:买卖IC网 > PDF目录19483 > ADSP-21375KSWZ-2B (Analog Devices Inc)IC DSP 32BIT 266MHZ 208-MQFP PDF资料下载

参数资料

| 型号: | ADSP-21375KSWZ-2B |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/56页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 266MHZ 208-MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 36 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI |

| 时钟速率: | 266MHz |

| 非易失内存: | ROM(256 kB) |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-LQFP 裸露焊盘 |

| 供应商设备封装: | 208-LQFP-EP(28x28) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

�� �

�

�

�ADSP-21371� /� ADSP-21375�

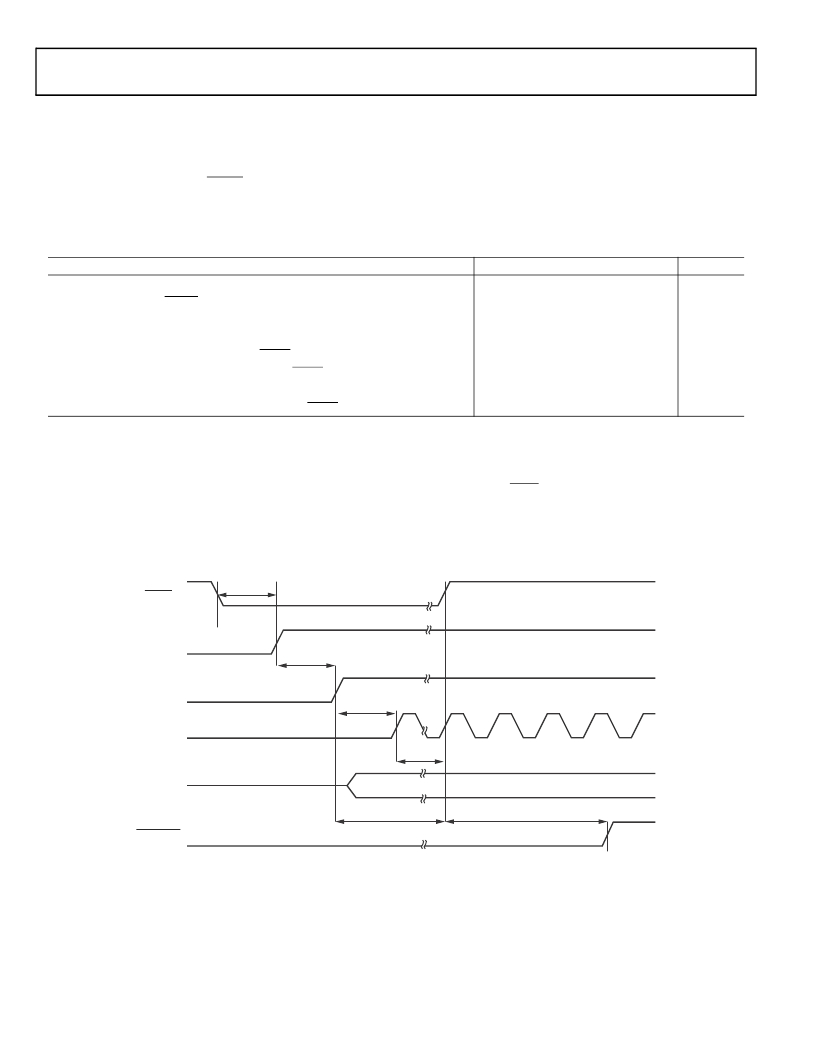

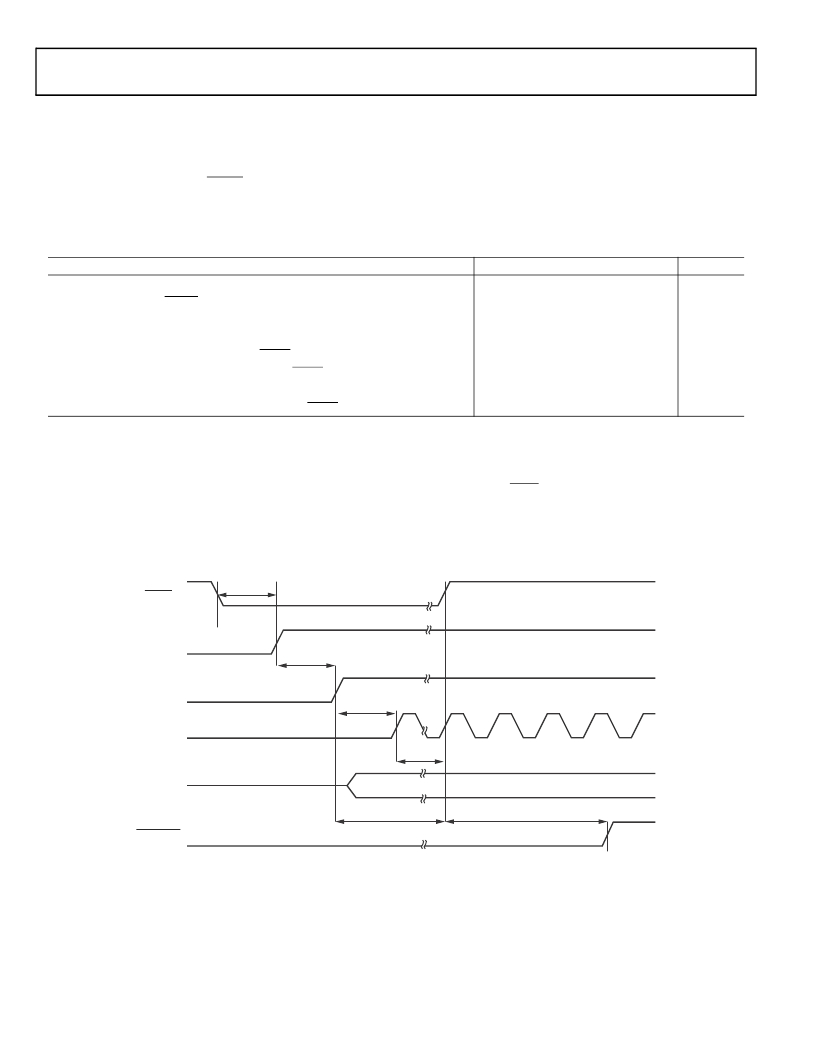

�Power-Up� Sequencing�

�The� timing� requirements� for� processor� startup� are� given� in�

��Note� that� during� power-up,� a� leakage� current� of� approximately�

�200� μA� may� be� observed� on� the� RESET� pin.� This� leakage� current�

�results� from� the� weak� internal� pull-up� resistor� on� this� pin� being�

�enabled� during� power-up.�

�Table� 13.� Power� Up� Sequencing� Timing� Requirements� (Processor� Startup)�

�Parameter�

�Min�

�Max�

�Unit�

�Timing� Requirements�

�t� RSTVDD�

�RESET� Low� Before� V� DDINT� /V� DDEXT� On�

�0�

�ns�

�t� IVDDEVDD�

�V� DDINT� on� Before� V� DDEXT�

�–50�

�+200�

�ms�

�t� CLKVDD�

�t� CLKRST�

�t� PLLRST�

�1�

�CLKIN� Valid� After� V� DDINT� /V� DDEXT� Valid�

�CLKIN� Valid� Before� RESET� Deasserted�

�PLL� Control� Setup� Before� RESET� Deasserted�

�0�

�10� 2�

�20� 3�

�200�

�ms�

�μs�

�μs�

�Switching� Characteristic�

�t� CORERST�

�Core� Reset� Deasserted� After� RESET� Deasserted�

�4096� � t� CK� +� 2� � t� CCLK� 4,� 5�

�1�

�2�

�3�

�4�

�5�

�Valid� V� DDINT� /V� DDEXT� assumes� that� the� supplies� are� fully� ramped� to� their� 1.2� and� 3.3� volt� rails.� Voltage� ramp� rates� can� vary� from� microseconds� to� hundreds� of� milliseconds�

�depending� on� the� design� of� the� power� supply� subsystem.�

�Assumes� a� stable� CLKIN� signal,� after� meeting� worst-case� startup� timing� of� crystal� oscillators.� Refer� to� your� crystal� oscillator� manufacturer's� datasheet� for� startup� time.� Assume�

�a� 25� ms� maximum� oscillator� startup� time� if� using� the� XTAL� pin� and� internal� oscillator� circuit� in� conjunction� with� an� external� crystal.�

�Based� on� CLKIN� cycles.�

�Applies� after� the� power-up� sequence� is� complete.� Subsequent� resets� require� a� minimum� of� four� CLKIN� cycles� for� RESET� to� be� held� low� in� order� to� properly� initialize� and�

�propagate� default� states� at� all� I/O� pins.�

�The� 4096� cycle� count� depends� on� t� SRST� specification� in� Table� 15� .� If� setup� time� is� not� met,� one� additional� CLKIN� cycle� may� be� added� to� the� core� reset� time,� resulting� in� 4097�

�cycles� maximum.�

�RESET�

�V� DDINT�

�V� DDEXT�

�t� RSTVDD�

�t� IVDDEVDD�

�t� CLKVDD�

�CLKIN�

�t� CLKRST�

�CLK_CFG1–0�

�RESETOUT�

�t� PLLRST�

�Figure� 5.� Power-Up� Sequencing�

�Rev.� D� |� Page� 20� of� 56� |� April� 2013�

�t� CORERST�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| SMK316B7682KF-T | CAP CER 6800PF 630V 10% X7R 1206 |

| ECC22DCAH | CONN EDGECARD 44POS R/A .100 SLD |

| XC95144XL-5TQ100C | IC CPLD 144 MCELL 3.3V 100-TQFP |

| VE-20F-CY-F2 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21375KSWZ-2B2 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor optimized for high performance audio processing |

| ADSP-21375KSWZ-2BX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21375KSZ-2B | 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT/40-BIT 266MHZ 266MIPS 208MQFP - Trays |

| ADSP-21375KSZ-2BX | 制造商:Analog Devices 功能描述:266 MHZ.PROC W/ON CHIPROM,S/PDIF PBFREE - Trays |

| ADSP-21375KSZ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

发布紧急采购,3分钟左右您将得到回复。