- 您现在的位置:买卖IC网 > PDF目录166397 > B900M24FXX12IT 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 PDF资料下载

参数资料

| 型号: | B900M24FXX12IT |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 |

| 文件页数: | 25/100页 |

| 文件大小: | 1547K |

| 代理商: | B900M24FXX12IT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

30

Lucent Technologies Inc.

B900

Advance Data Sheet

Baseband Signal Processor

July 1999

4 Hardware Architecture (continued)

4.6

Synchronous Serial Interface (SSI) (continued)

The SSI has two programmable registers, one 16-bit register for control and one 8-bit register for data. The 16-bit

control register, ssic, enables and configures the SSI for serial communication in the desired mode. It has control

fields (the EN, MSTR, SPOL, SPHA, SDOEN, SSNEN, and SCLK bits of the ssic register) and status fields (the

SDONE, WCOLL, and MODF bits of the ssic register). The 8-bit data register, ssid, is used for writing the byte to

be transmitted and reading the received byte.

Table 51 on page 60 shows the register structure of the SSI control registers ssic. Brief descriptions of the function

of each control bit are also given in the tables. Table 52 on page 61 shows the register structure of the SSI data reg-

ister ssid.

4.6.1 SSI Operation

The SPOL and SPHA bits in the SSI control register determine the mode of data transfer. Both of these bits control

the type of shift clock (SCK) generated. SPOL controls the polarity of SCK, and SPHA determines the phase at

which the serial transfer begins. The latter leads to a fundamentally different type of transfer with implications in sit-

uations where back-to-back byte transfer is required. The transfer formats may be different for different peripheral

devices but remain unchanged during a transfer between the master and the slave device. The SSI is flexible

enough to allow any desired configuration that conforms to the HC11 specifications.

The SSI generates an interrupt whenever a byte is successfully shifted in and copied to the read data buffer or

when a mode-fault occurs. The interrupts are enabled by the appropriate bits in the inc register, and their status is

posted in the ins register.

The SSI control register includes 3 bits, SDONE, WCOLL, and MODF, that can only be read by the processor. Their

values are written by the SSI. SDONE is a status flag that indicates the end of a transfer. The WCOLL flag indicates

a write was attempted to the SSI data register while a transfer was in progress. The MODF bit indicates a mode

fault. This occurs when the B900 SSI is configured as a master and its SSN line is pulled low. Another error condi-

tion can occur when the B900 is configured as a slave and a transfer is aborted by pulling SSN high before the

transfer is complete. This error condition is not indicated by the status flags.

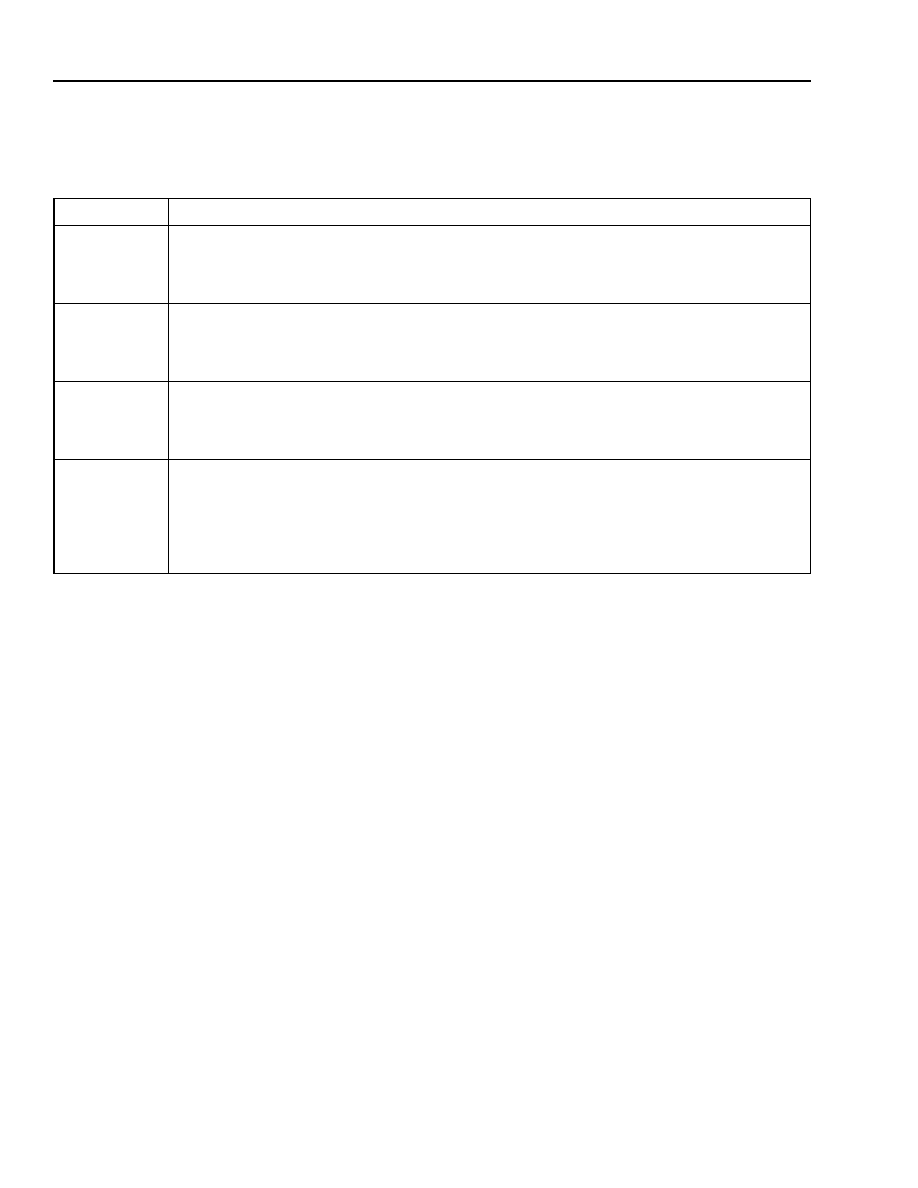

Table 17. SSI Pin Descriptions

Pin

Description

SCK

SSI Clock. Bidirectional. If SSI is configured in master mode, this pin is an output providing a

clock to the slave devices. If SSI is configured in slave mode, this pin is an input that takes in the

serial clock. This pin is multiplexed with IOPC5 (if the ssic register disables the SSI

(bit 15 = 0), then this pin is used for IOPC5).

MDOSDI

Master Data Out/Slave Data In. Bidirectional. If the SSI is configured in master mode, this pin

is the serial data output. If the SSI is configured in slave mode, this pin is the serial data input.

This pin is multiplexed with IOPC6 (if the ssic register disables the SSI (bit 15 = 0), then this pin

is used for IOPC6).

MDISDO

Master Data In/Slave Data Out. Bidirectional. If SSI is configured in master mode, this pin is

an input and samples serial data supplied by the master device. If SSI is configured in slave

mode, this pin is the serial data output. This pin is multiplexed with IOPC7 (if the ssic register

disables the SSI (bit 15 = 0), then this pin is used for IOPC7).

SSN

Serial Select. Input. Negative assertion. When SSI is configured as a slave, the assertion of

SSN signals the slave that is being addressed to transfer data with the master device. If this pin

is asserted while SSI is configured as a master, a mode fault will be detected by SSI. This pin is

multiplexed with IOPC4 (if the ssic register disables the SSI (bit 15 = 0), or if the ssic register

configures the SSI for master mode (bit 14 = 1) and the SSN input is disabled (bit 10 = 0), then

this pin is used for IOPC4).

相关PDF资料 |

PDF描述 |

|---|---|

| B900J24PXX12I | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| B901 | 制造商:EDAL 制造商全称:EDAL 功能描述:Silicon Bridge Rectifier |

| B901 10.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 10.0MM |

| B901 4.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 4.0MM |

| B901 5.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 5.0MM |

| B901 8.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 8.0MM |

发布紧急采购,3分钟左右您将得到回复。