- 您现在的位置:买卖IC网 > PDF目录166397 > B900M24FXX12IT 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 PDF资料下载

参数资料

| 型号: | B900M24FXX12IT |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 |

| 文件页数: | 50/100页 |

| 文件大小: | 1547K |

| 代理商: | B900M24FXX12IT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

Lucent Technologies Inc.

53

Advance Data Sheet

B900

July 1999

Baseband Signal Processor

5 Software Architecture (continued)

5.2

Register Settings (continued)

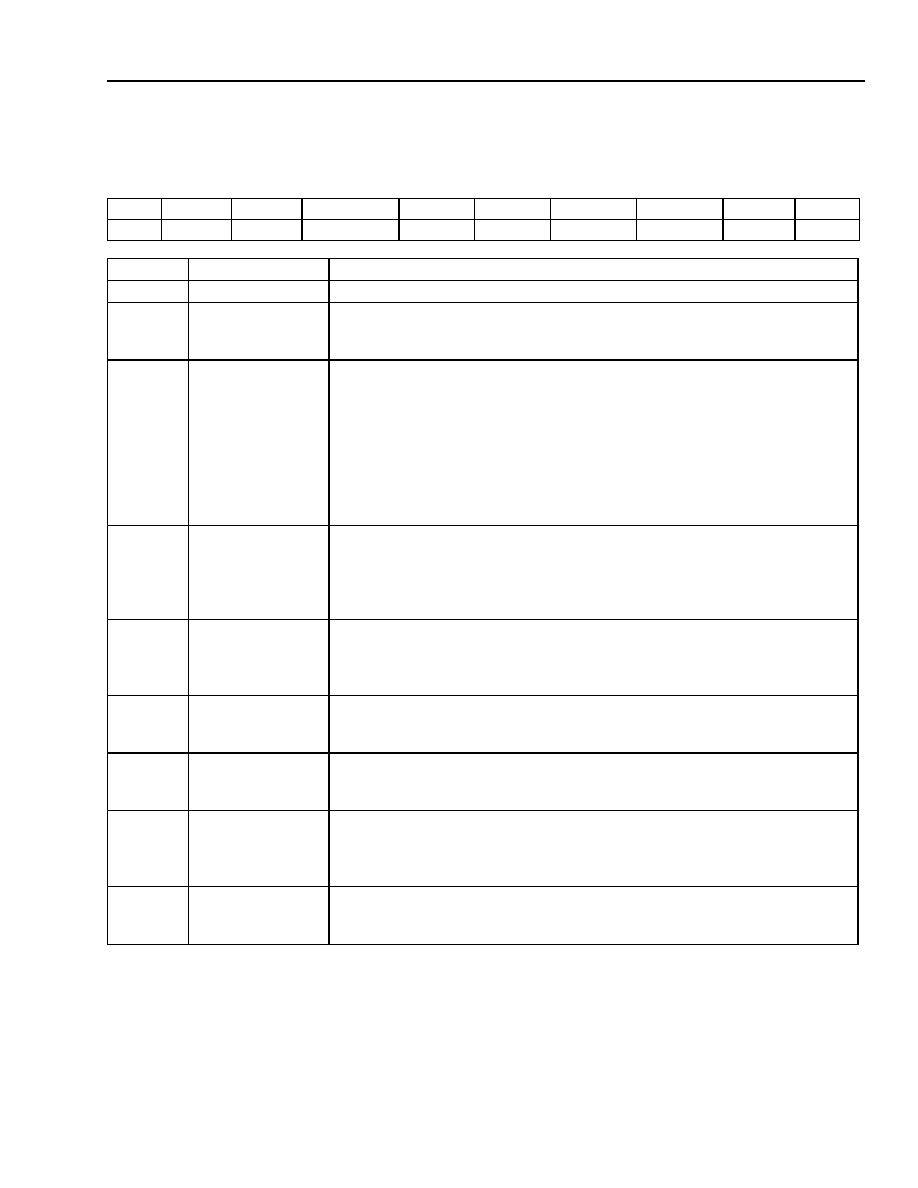

Table 41. clkc Register Fields

Bit

15—13

12

11—8

7—6

5—4

3

2

1

0

Field

Res

PFIVOLT DOUT MUX

SLOMUX

SELCLK

STOPCLK

ROSCDIS

OSCDIS

PLLEN

Bit

Field

Description

15—13

Reserved

Write with 0, read as 0.

12

PFIVOLT

Voltage select:

0 = 3 V.

1 = 5 V.

11—8

DOUT MUX[3:0]

DOUT source selection:

0000 = logic 0 selected to DOUT.

0001 = input crystal/clock (CLKIN) selected to DOUT.

0010 = low-frequency clock (CLKLOW) selected to DOUT.

0011 = wait-stated B900 clock (CLKWAIT) selected to DOUT.

0100 = free-running B900 clock (CLKFREE) selected to DOUT.

0101 = slow, smooth MUX output selected to DOUT (CLKCORE2X).

0110 = logic 0 selected to DOUT.

0111 = logic 1 selected to DOUT.

7—6

SLOMUX[1:0]

Low-frequency clock source selection (CLKLOW):

00 = chip input clock (CLKIN) divided by 4.

01 = chip input clock (CLKIN) divided by 32.

10 = chip input clock (CLKIN) divided by 128.

11 = internal ring oscillator (CLKRING).

5—4

SELCLK[1:0]*

* It is recommended that the 2 bits of the SELCLK field be changed one at a time to prevent the possibility of an intermediate clock switch

before switching to the desired destination clock. For example, to switch the clock selection back and forth between the low-frequency clock

(CLKLOW) and the high-frequency PLL output (CLKPLL), the more significant bit of SELCLK (clkc[5]) should be set to one, allowing the less

significant bit of SELCLK (clkc[4]) to be toggled on and off without the possibility of an intermediate clock switch.

Select the 2X core clock (CLKCORE2X) (as long as STOPCLK = 0):

00 = select input clock (CLKIN).

X1 = select PLL output (CLKPLL).

10 = select low-frequency clock (CLKLOW) as selected by SLOMUX[1:0].

3

STOPCLK

Stop B900 core clock (CLKCORE2X):

0 = clock runs as normal.

1 = disable 2X B900 input core clock.

2

ROSCDIS

Ring oscillator disable:

0 = enable the internal ring oscillator clock (CLKRING).

1 = disable the internal ring oscillator clock (CLKRING).

1

OSCDIS

This bit should not be set if the internal crystal oscillator is bypassed, i.e., OSCBYP pin = 1. Also note that when this bit is set, it will not take

effect until after CLKRING is selected and is sourcing CLKCORE2X.

Oscillator disable (this bit should only be set if the oscillator is not bypassed,

i.e., OSCBYP pin = 0):

0 = enable the crystal oscillator clock.

1 = disable the crystal oscillator clock.

0

PLLEN

This bit is overridden if it is cleared to zero and if the PLL output (CLKPLL) is selected as the 2X core clock (if SELCLK[0] = 1).

Phase-locked loop enable:

0 = disable PLL circuitry.

1 = enable PLL to operate.

相关PDF资料 |

PDF描述 |

|---|---|

| B900J24PXX12I | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| B901 | 制造商:EDAL 制造商全称:EDAL 功能描述:Silicon Bridge Rectifier |

| B901 10.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 10.0MM |

| B901 4.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 4.0MM |

| B901 5.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 5.0MM |

| B901 8.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 8.0MM |

发布紧急采购,3分钟左右您将得到回复。