- 您现在的位置:买卖IC网 > PDF目录166397 > B900M24FXX12IT 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 PDF资料下载

参数资料

| 型号: | B900M24FXX12IT |

| 元件分类: | 数字信号处理 |

| 英文描述: | 0-BIT, 59.88 MHz, OTHER DSP, PQCC44 |

| 文件页数: | 73/100页 |

| 文件大小: | 1547K |

| 代理商: | B900M24FXX12IT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页当前第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

74

Lucent Technologies Inc.

B900

Advance Data Sheet

Baseband Signal Processor

July 1999

7 Electrical Requirements and Characteristics (continued)

* Lock-in time represents the time following assertion of the PLLEN bit of the pllc register during which the PLL output clock is unstable. The

B900 must operate from the CLKIN input clock or from CLKLOW while the PLL is locking.

7.1

Typical Power Dissipation

Power dissipation is highly dependent on program activity and the frequency of operation. Table 95 lists typical

power dissipation on a module-by-module basis and consists of preliminary data that is subject to change. For ana-

log modules, this data assumes the recommended external circuitry is being used. For digital modules, it refers to

internal power only, i.e., Table 95 does not account for activity on digital I/O pins. The total analog and internal digi-

tal power can be calculated by adding the sum of the modules that have been enabled. For example, the lowest

power dissipation can be achieved by turning everything off except for the internal low-power oscillator and setting

the stop-clock bit. In this case, the total power would be 62 W at 3.1 V.

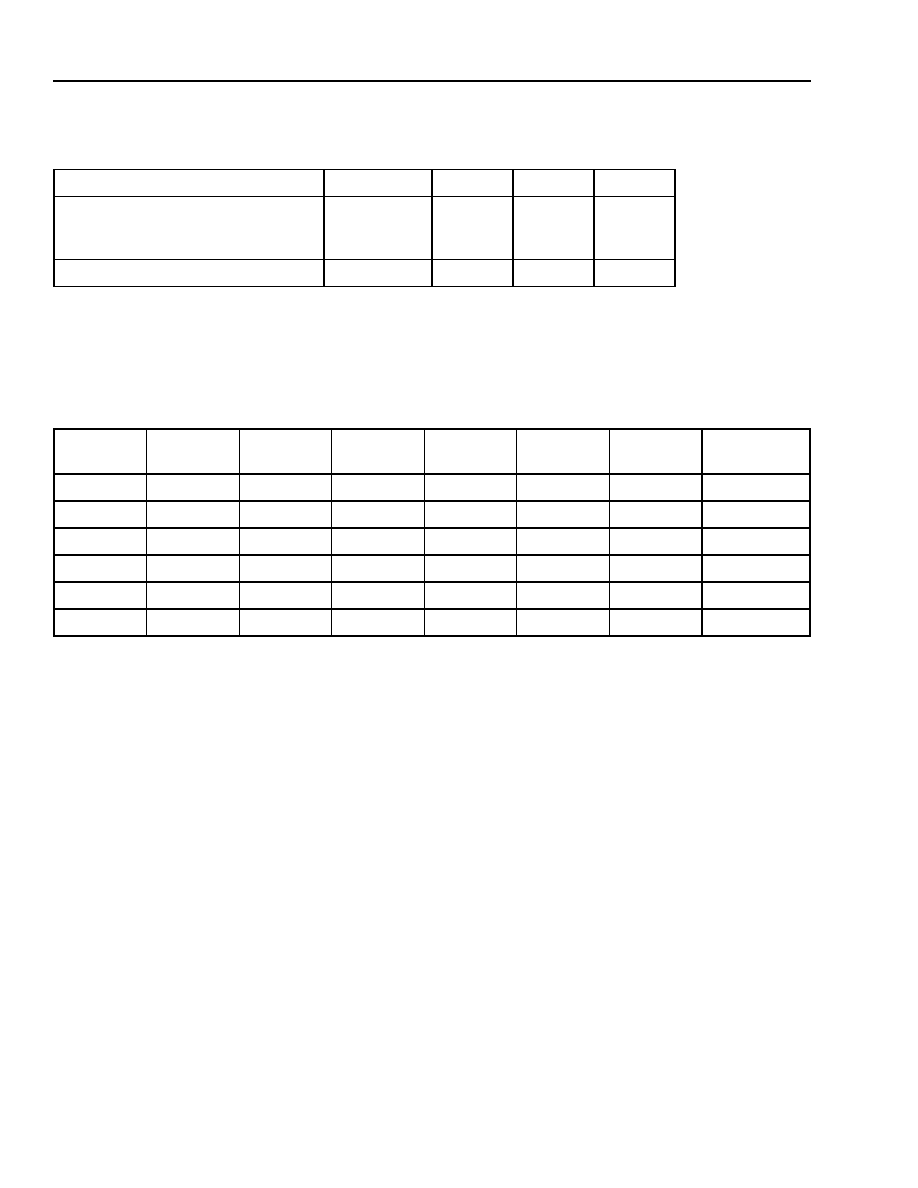

Table 93. PLL Electrical Specifications, VCO Frequency Ranges

Parameter

Symbol

Min

Max

Unit

VCO Frequency Range*:

VDD = 3 V

± 10%

VDD = 5 V

± 10%

* The M and N counter values in the pllc register must be set so that the VCO will operate in the appropriate range,

where

.

Choose the lowest value of N and then the appropriate value of M for internal MIPS rate =

fVCO

50

150

200

MHz

Input Jitter at CKI

—

200

ps-rms

Table 94. PLL Electrical Specifications and Register Settings

Voltage

(Volts)

M

pllc[5:0]

K

pllc[8:6]

N

pllc[10:9]

ICP

pllc[13:11]

LF

pllc[15:14]

PFIVOLT

clkc[12]

Typical Lock

Time (s)*

3.0—3.6

>28

0—7

0—1

101

11

0

8—20

3.0—3.6

19—28

0—7

0—1

110

10

0

8—20

3.0—3.6

<19

0—7

0—1

110

01

0

8—20

4.5—5.5

>28

0—7

0—1

110

11

1

8—20

4.5—5.5

19—28

0—7

0—1

111

10

1

8—20

4.5—5.5

<19

0—7

0—1

111

01

1

8—20

VC Ofreq

CLKINfreq

m2

+

()

N1

+

()

-----------------

×

=

I

( nputClock m 2 )

+

()

2K

(

1

) N1 ))

+

(

+

(

----------------------------------------------------------

相关PDF资料 |

PDF描述 |

|---|---|

| B900J24PXX12I | 0-BIT, 80 MHz, OTHER DSP, PQFP44 |

| B900J24FXX12IT | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| BA00CC0WCP-V5 | 1A Low Dropout Voltage Regulator with Shut Down Switch(Adustable Voltage) |

| BA10E6 | COPPER ALLOY, TIN FINISH, RING TERMINAL |

| BA12004 | 0.5 A, 7 CHANNEL, NPN, Si, POWER TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| B901 | 制造商:EDAL 制造商全称:EDAL 功能描述:Silicon Bridge Rectifier |

| B901 10.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 10.0MM |

| B901 4.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 4.0MM |

| B901 5.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 5.0MM |

| B901 8.0MM | 制造商:DORMER TOOLS 功能描述:M/C REAMER B901 8.0MM |

发布紧急采购,3分钟左右您将得到回复。