- 您现在的位置:买卖IC网 > PDF目录69013 > M37274MA-XXXSP 8-BIT, MROM, MICROCONTROLLER, PDIP52 PDF资料下载

参数资料

| 型号: | M37274MA-XXXSP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, MICROCONTROLLER, PDIP52 |

| 封装: | 0.600 INCH, 1.778 MM PITCH, SHRINK, PLASTIC, DIP-52 |

| 文件页数: | 41/131页 |

| 文件大小: | 2049K |

| 代理商: | M37274MA-XXXSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页

17

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER

and ON-SCREEN DISPLAY CONTROLLER

M37274MA-XXXSP

PRELIMINARY

Notice:

This

is not

a final

specification.

Some

paramentic

limits

are

subject

to change.

MITSUBISHI MICROCOMPUTERS

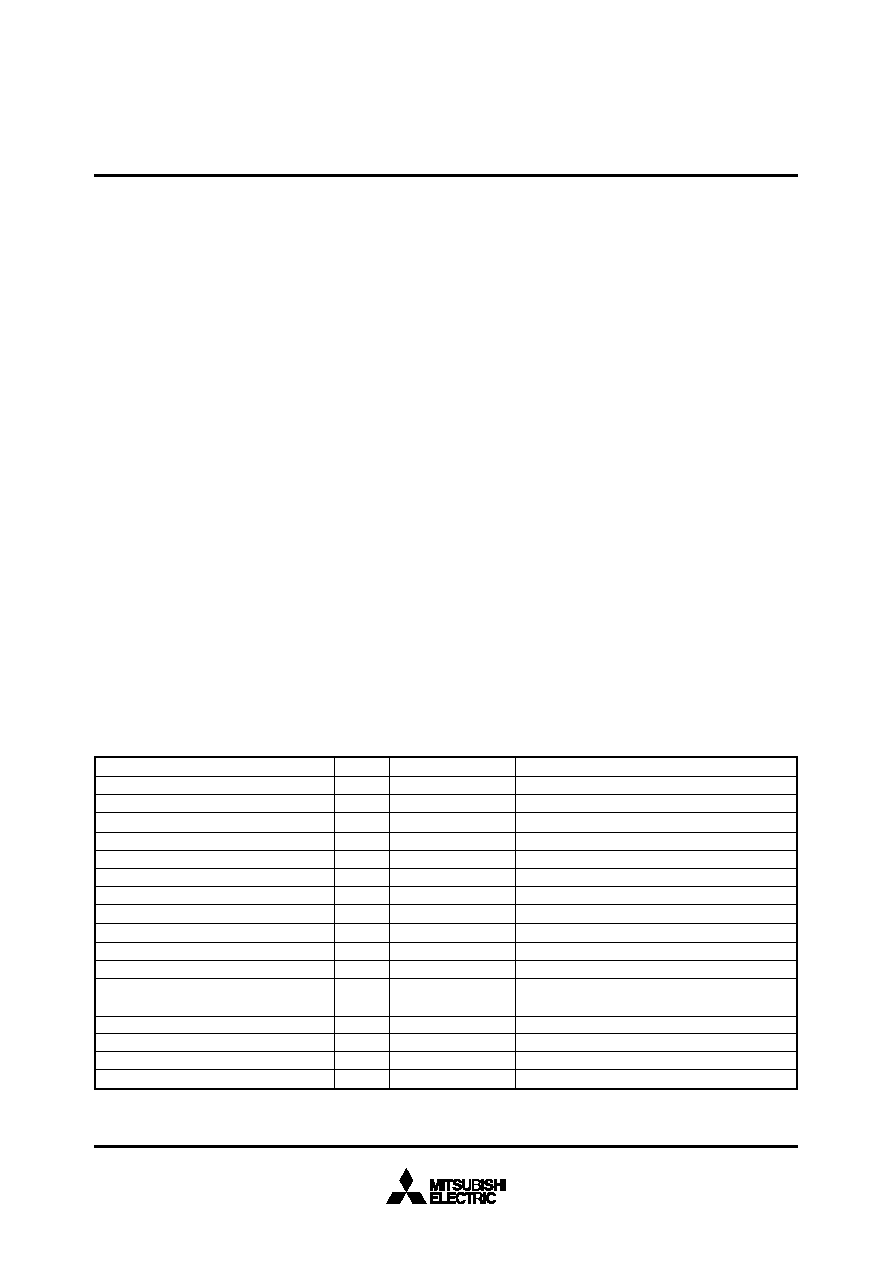

INTERRUPTS

Interrupts can be caused by 18 different sources consisting of 4 ex-

ternal, 12 internal, 1 software, and reset. Interrupts are vectored in-

terrupts with priorities as shown in Table 1. Reset is also included in

the table because its operation is similar to an interrupt.

When an interrupt is accepted,

(1) The contents of the program counter and processor status

register are automatically stored into the stack.

(2) The interrupt disable flag I is set to “1” and the corresponding

interrupt request bit is set to “0.”

(3) The jump destination address stored in the vector address enters

the program counter.

Other interrupts are disabled when the interrupt disable flag is set to

“1.”

All interrupts except the BRK instruction interrupt have an interrupt

request bit and an interrupt enable bit. The interrupt request bits are

in interrupt request registers 1 and 2 and the interrupt enable bits are

in interrupt control registers 1 and 2. Figure 11 shows the interrupt-

related registers.

Interrupts other than the BRK instruction interrupt and reset are ac-

cepted when the interrupt enable bit is “1,” interrupt request bit is “1,”

and the interrupt disable flag is “0.” The interrupt request bit can be

set to “0” by a program, but not set to “1.” The interrupt enable bit can

be set to “0” and “1” by a program.

Reset is treated as a non-maskable interrupt with the highest priority.

Figure 10 shows interrupt control.

Interrupt Causes

(1) VSYNC and OSD interrupts

The VSYNC interrupt is an interrupt request synchronized with

the vertical sync signal.

The OSD interrupt occurs after character block display to the

CRT is completed.

(2) INT1, INT2, INT3 interrupts

With an external interrupt input, the system detects that the level

of a pin changes from “L” to “H” or from “H” to “L,” and generates

an interrupt request. The input active edge can be selected by

bits 3, 4 and 6 of the interrupt input polarity register (address

021216) : when this bit is “0,” a change from “L” to “H” is detected;

when it is “1,” a change from “H” to “L” is detected. Note that all

bits are cleared to “0” at reset.

(3) Timer 1, 2, 3 and 4 interrupts

An interrupt is generated by an overflow of timer 1, 2, 3 or 4.

(4) Serial I/O interrupt

This is an interrupt request from the clock synchronous serial

I/O function.

(5) f(XIN)/4096 interrupt

This interrupt occurs regularly with a f(XIN)/4096 period. Set bit 0

of the PWM mode register 1 to “0.”

(6) Data slicer interrupt

An interrupt occurs when slicing data is completed.

(7) Multi-master I2C-BUS interface interrupt

This is an interrupt request related to the multi-master I2C-BUS

interface.

(8) A-D conversion interrupt

An interrupt occurs at the completion of A-D conversion. Since

A-D conversion interrupt and the INT3 interrupt share the same

vector, an interrupt source is selected by bit 7 of the interrupt

interval determination control register (address 021216).

Vector Addresses

FFFF16, FFFE16

FFFD16, FFFC16

FFFB16, FFFA16

FFF916, FFF816

FFF716, FFF616

FFF516, FFF416

FFF316, FFF216

FFF116, FFF016

FFEF16, FFEE16

FFED16, FFEC16

FFEB16, FFEA16

FFE916, FFE816

FFE716, FFE616

FFE516, FFE416

FFE316, FFE216

FFDF16, FFDE16

Interrupt Source

Reset

OSD interrupt

INT1 interrupt

Data slicer interrupt

Serial I/O interrupt

Timer 4 interrupt

f(XIN)/4096 interrupt

VSYNC interrupt

Timer 3 interrupt

Timer 2 interrupt

Timer 1 interrupt

A-D convertion INT3 interrupt

INT2 interrupt

Multi-master I2C-BUS interface interrupt

Timer 5 6 interrupt

BRK instruction interrupt

Remarks

Non-maskable

Active edge selectable

Software switch by software (See note)/

When selecting INT3 interrupt, active edge selectable.

Active edge selectable

Software switch by software (See note)

Non-maskable (software interrupt)

Table 1. Interrupt Vector Addresses and Priority

Priority

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Note : Switching a source during a program causes an unnecessary interrupt occurs. Accordingly, set a source at initializing of program.

相关PDF资料 |

PDF描述 |

|---|---|

| M37373M8-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP52 |

| M37409M2-XXXFP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP56 |

| M37413E6HXXXFP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37413M4-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37420M4-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M37276MF248SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF2575P | 制造商:MITSUBISHI 功能描述:* |

| M37276MF260SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF300SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF301SP | 制造商:MITSUBISHI 功能描述:* |

发布紧急采购,3分钟左右您将得到回复。