- 您现在的位置:买卖IC网 > PDF目录385639 > MT48V2M32LFFC (Micron Technology, Inc.) 512K x 32 x 4 banks 2.5V SDRAM(2.5V,512K x 32 x 4组同步动态RAM) PDF资料下载

参数资料

| 型号: | MT48V2M32LFFC |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | 512K x 32 x 4 banks 2.5V SDRAM(2.5V,512K x 32 x 4组同步动态RAM) |

| 中文描述: | 为512k × 32 × 4银行2.5V的内存电压(2.5V,512K采样× 32 × 4组同步动态RAM)的 |

| 文件页数: | 24/50页 |

| 文件大小: | 1058K |

| 代理商: | MT48V2M32LFFC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

24

64Mb: x32 SDRAM, 2.5V

BatRam_25V.p65 – Rev. 0.7, Pub. 2/01

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc.

64Mb: x32, 2.5V

SDRAM

PRELIMINARY

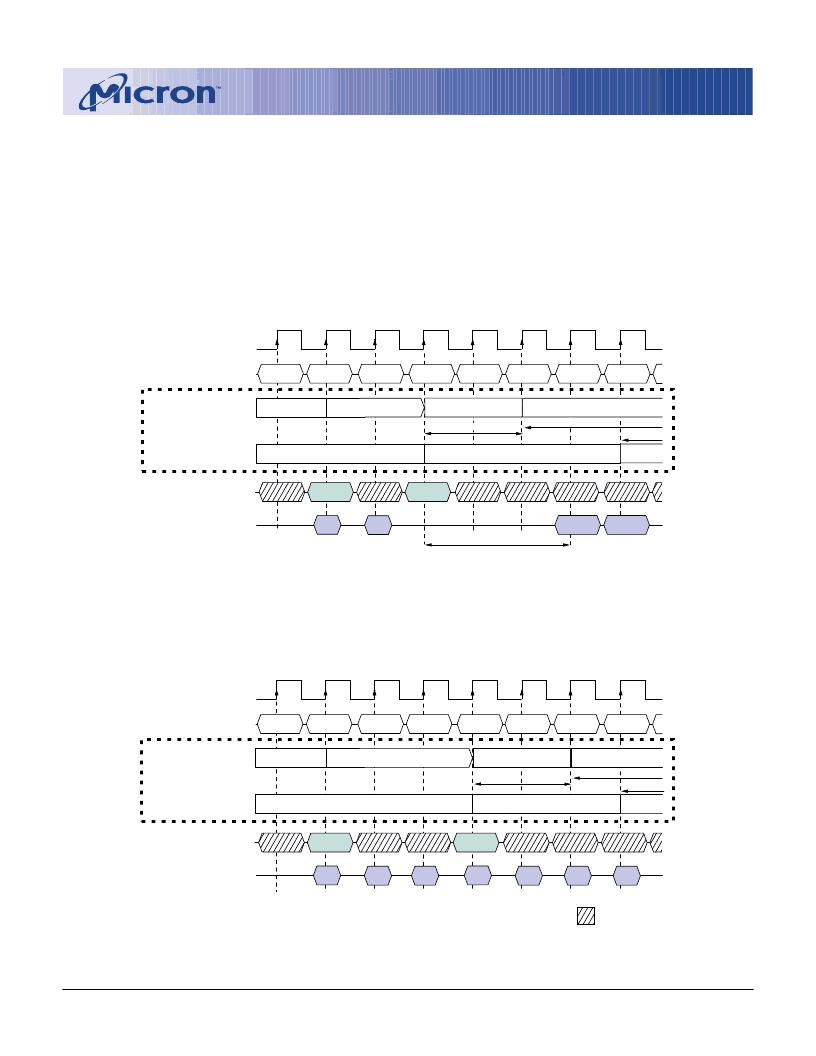

WRITE with Auto Precharge

3. Interrupted by a READ (with or without auto

precharge): A READ to bank

m

will interrupt a WRITE

on bank

n

when registered, with the data-out ap-

pearing CAS latency later. The PRECHARGE to bank

n will begin after

t

WR is met, where

t

WR begins when

the READ to bank m is registered. The last valid

WRITE to bank n will be data-in registered one clock

prior to the READ to bank m (Figure 26).

4. Interrupted by a WRITE (with or without auto

precharge): A WRITE to bank

m

will interrupt a

WRITE on bank

n

when registered. The PRECHARGE

to bank

n

will begin after

t

WR is met, where

t

WR

begins when the WRITE to bank

m

is registered. The

last valid data WRITE to bank

n

will be data regis-

tered one clock prior to a WRITE to bank 1 (Figure

27).

CLK

DQ

T2

T1

T4

T3

T6

T5

T0

COMMAND

WRITE - AP

BANK

n

NOP

NOP

NOP

NOP

D

IN

a

+ 1

D

IN

a

NOP

NOP

T7

BANK

n

BANK

m

ADDRESS

NOTE:

1. DQM is LOW.

BANK

n

,

COL

a

BANK

m

,

COL

d

READ - AP

BANK

m

Internal

States

t

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

Page Active

READ with Burst of 4

t

tRP - BANK

m

D

OUT

d

D

OUT

d

+ 1

CAS Latency = 3 (BANK

m

)

RP - BANK

n

WR - BANK

n

Figure 26

WRITE With Auto Precharge Interrupted By A READ

DON’T CARE

CLK

DQ

T2

T1

T4

T3

T6

T5

T0

COMMAND

WRITE - AP

BANK

n

NOP

NOP

NOP

NOP

D

IN

d

+ 1

D

IN

d

D

IN

a

+ 1

D

IN

a

+ 2

D

IN

a

D

IN

d

+ 2

D

IN

d

+ 3

NOP

T7

BANK

n

BANK

m

ADDRESS

NOP

NOTE:

1. DQM is LOW.

BANK

n

,

COL

a

BANK

m

,

COL

d

WRITE - AP

BANK

m

Internal

States

t

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

Page Active

WRITE with Burst of 4

Write-Back

WR - BANK

n

tRP - BANK

n

tWR - BANK

m

Figure 27

WRITE With Auto Precharge Interrupted By A WRITE

相关PDF资料 |

PDF描述 |

|---|---|

| MT48V4M32LFFC | SYNCHRONOUS DRAM |

| MT49H16M16 | THERMISTOR PTC 100OHM 110DEG RAD |

| MT49H16M16FM | REDUCED LATENCY DRAM RLDRAM |

| MT49H8M32 | THERMISTOR PTC 100OHM 120DEG RAD |

| MT49H8M32FM | REDUCED LATENCY DRAM RLDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT48V32M16S2FG-10 | 制造商:Micron Technology Inc 功能描述:32MX16 SSDRAM PLASTIC 2BOC 2.5V - Trays |

| MT48V32M16S2FG-8 ES | 制造商:Micron Technology Inc 功能描述:DRAM CHIP MOBILE SDRAM 512MBIT 2.5V 54FBGA - Bulk |

发布紧急采购,3分钟左右您将得到回复。