- 您现在的位置:买卖IC网 > PDF目录378057 > PM8621-BIAP (PMC-SIERRA INC) NSE-8G⑩ Standard Product Data Sheet Preliminary PDF资料下载

参数资料

| 型号: | PM8621-BIAP |

| 厂商: | PMC-SIERRA INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | NSE-8G⑩ Standard Product Data Sheet Preliminary |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA480 |

| 封装: | 35 X 35 MM, 1.47 MM HEIGHT, UBGA-480 |

| 文件页数: | 59/184页 |

| 文件大小: | 1122K |

| 代理商: | PM8621-BIAP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页

NSE-8G Standard Product Data Sheet

Preliminary

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

Document ID: PMC-2010850, Issue 1

58

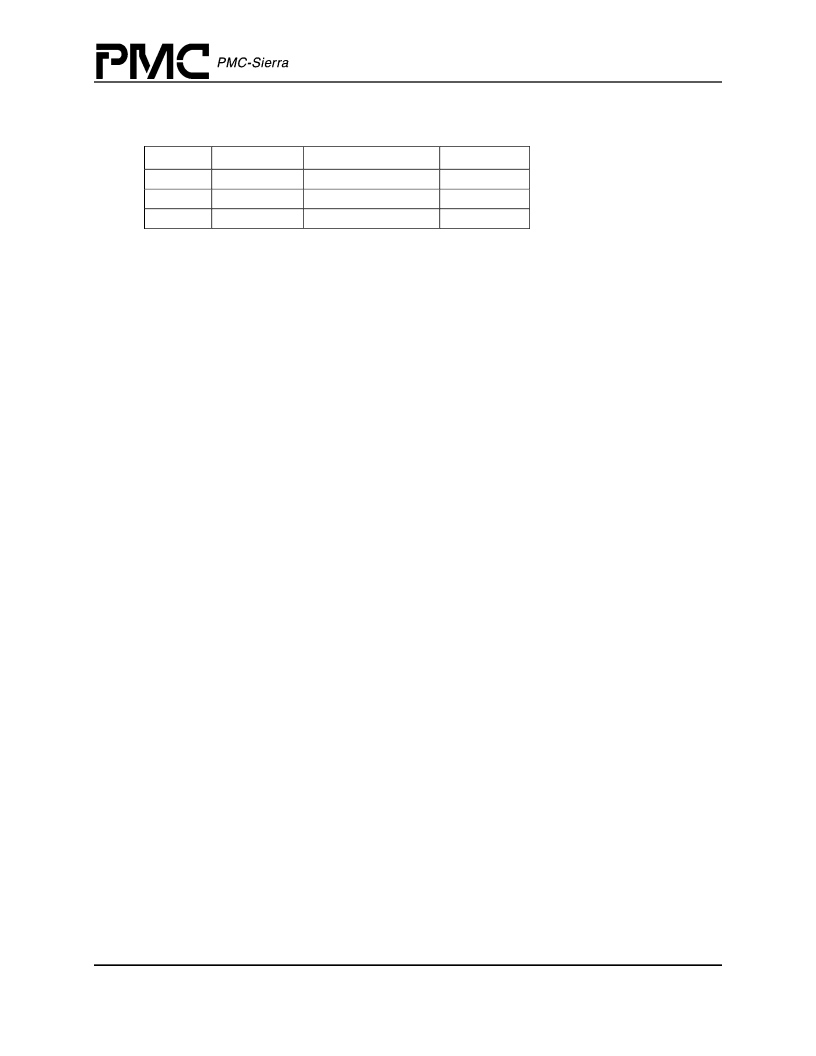

Register 000H: NSE-8G Master Reset

Bit

Type

Function

Default

Bit 31

R/W

DRESET

0

Bit 30

R/W

ARESET

0

Bit 29:0

R

Unused

X

This register allows separate software reset of digital and analog circuitry on the NSE.

ARESET

The ARESET bit allows the analog circuitry in the NSE-8G to be reset under software

control. If the ARESET bit is a logic one, all the NSE-8G analog circuitry is held in reset.

ARESET must be held at logic one for at least 100us to ensure correct reset of the CSU. This

bit is not self-clearing. Therefore, a logic zero must be written to bring the NSE-8G out of

reset. Holding the NSE-8G in a reset state places it into a low power, analog stand-by mode.

A hardware reset clears the ARESET bit, thus negating the analog software reset.

DRESET

The DRESET bit allows the digital circuitry in the NSE-8G to be reset under software

control. If the DRESET bit is a logic one, all the NSE-8G digital circuitry is held in reset.

This bit is not self-clearing. Therefore, a logic zero must be written to bring the NSE-8G out

of reset. Holding the NSE-8G in a reset state places it into a low power, digital stand-by

mode. A hardware reset clears the DRESET bit, thus negating the digital software reset.

相关PDF资料 |

PDF描述 |

|---|---|

| PM9311 | Enhanced TT1TM Switch Fabric |

| PM9311-UC | ENHANCED TT1⑩ SWITCH FABRIC |

| PM9312 | Enhanced TT1TM Switch Fabric |

| PM9312-UC | ENHANCED TT1⑩ SWITCH FABRIC |

| PM9313 | Enhanced TT1TM Switch Fabric |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PM87 | 制造商:FERROXCUBE 制造商全称:Ferroxcube International Holding B.V. 功能描述:PM cores |

| PM87/70-3C94 | 制造商:Yageo / Ferroxcube 功能描述:FERRITE CORE PM 3C94 制造商:Yageo / Ferroxcube 功能描述:FERRITE CORE, PM, 3C94, Core Size:PM87, Material Grade:3C94, Effective Magnetic Path Length:146mm, Ae Effective Cross Section Area:910mm2, Inductance Factor Al:15000nH, SVHC:No SVHC (20-Jun-2013), External Depth:70mm, External , RoHS Compliant: Yes |

| PM871 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| PM872 | 制造商:ARTESYN 制造商全称:Artesyn Technologies 功能描述:Single and dual output 10 to 12 Watt Nominal input DC/DC converters |

| PM87-3C90 | 制造商:FERROXCUBE 制造商全称:Ferroxcube International Holding B.V. 功能描述:PM cores |

发布紧急采购,3分钟左右您将得到回复。