- 您现在的位置:买卖IC网 > PDF目录225025 > RC28F160C3BD70 (INTEL CORP) 1M X 16 FLASH 3V PROM, 70 ns, PBGA64 PDF资料下载

参数资料

| 型号: | RC28F160C3BD70 |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | 1M X 16 FLASH 3V PROM, 70 ns, PBGA64 |

| 封装: | BGA-64 |

| 文件页数: | 42/72页 |

| 文件大小: | 1083K |

| 代理商: | RC28F160C3BD70 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Intel Advanced+ Boot Block Flash Memory (C3)

Datasheet

Intel Advanced+ Boot Block Flash Memory (C3)

May 2005

Order Number: 290645, Revision: 023

47

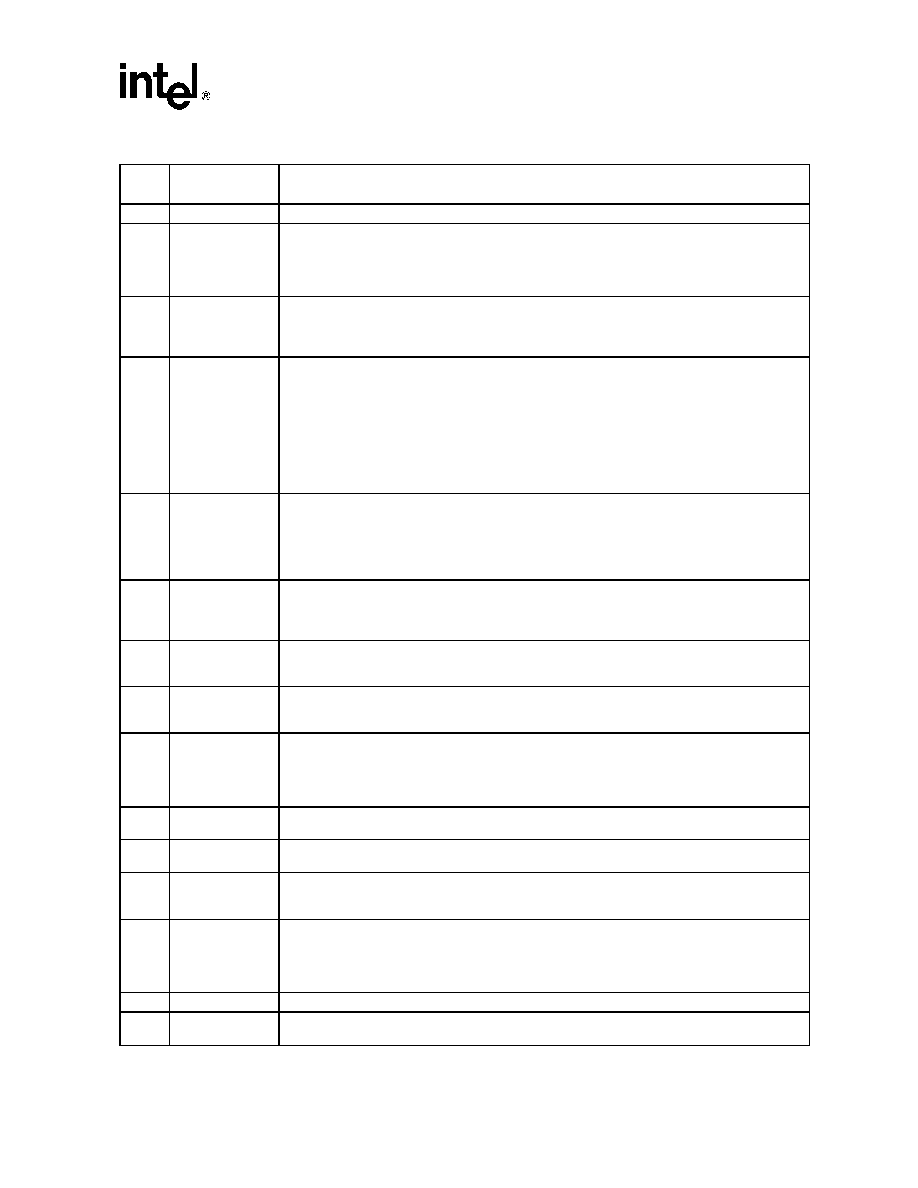

Table 23.

Command Codes and Descriptions

Code

(HEX)

Device Mode

Command Description

FF

Read Array

This command places the device in read-array mode, which outputs array data on the data pins.

40

Program Set-Up

This is a two-cycle command. The first cycle prepares the CUI for a program operation. The

second cycle latches addresses and data information and initiates the WSM to execute the

Program algorithm. The flash outputs Status Register data when CE# or OE# is toggled. A Read

Array command is required after programming to read array data. See Section 10.2, “Program

20

Erase Set-Up

This is a two-cycle command. It prepares the CUI for the Erase Confirm command. If the next

command is not an Erase Confirm command, then the CUI will (a) set both SR.4 and SR.5 to “1,”

(b) place the device into the read-Status Register mode, and (c) wait for another command. See

D0

Erase Confirm

Program/Erase

Resume

Unlock Block

If the previous command was an Erase Set-Up command, then the CUI will close the address and

data latches and begin erasing the block indicated on the address pins. During program/erase, the

device will respond only to the Read Status Register, Program Suspend and Erase Suspend

commands, and will output Status Register data when CE# or OE# is toggled.

If a Program or Erase operation was previously suspended, this command will resume that

operation.

If the previous command was Block Unlock Set-Up, the CUI will latch the address and unlock the

block indicated on the address pins. If the block had been previously set to Lock-Down, this

operation will have no effect. (See Section 11.1)

B0

Program Suspend

Erase Suspend

Issuing this command will begin to suspend the currently executing Program/Erase operation. The

Status Register will indicate when the operation has been successfully suspended by setting either

the program-suspend SR[2] or erase-suspend SR[6] and the WSM status bit SR[7] to a “1”

(ready). The WSM will continue to idle in the SUSPEND state, regardless of the state of all input-

control pins except RP#, which will immediately shut down the WSM and the remainder of the chip

if RP# is driven to VIL. See Sections 3.2.5.1 and 3.2.6.1.

70

Read Status

Register

This command places the device into read-Status Register mode. Reading the device will output

the contents of the Status Register, regardless of the address presented to the device. The device

automatically enters this mode after a Program or Erase operation has been initiated. See Section

50

Clear Status

Register

The WSM can set the block-lock status SR[1], VPP Status SR[3], program status SR[4], and erase-

status SR[5] bits in the Status Register to “1,” but it cannot clear them to “0.” Issuing this command

clears those bits to “0.”

90

Read Identifier

This command puts the device into the read-identifier mode so that reading the device will output

the manufacturer/device codes or block-lock status. See Section 10.1.2, “Read Identifier” on

60

Block Lock,

Block Unlock,

Block Lock-Down

Set-Up

This command prepares the CUI for block-locking changes. If the next command is not Block

Unlock, Block Lock, or Block Lock-Down, then the CUI will set both the program and erase-Status

Register bits to indicate a command-sequence error. See Section 11.0, “Security Modes” on

01

Lock-Block

If the previous command was Lock Set-Up, the CUI will latch the address and lock the block

indicated on the address pins. (See Section 11.1)

2F

Lock-Down

If the previous command was a Lock-Down Set-Up command, the CUI will latch the address and

lock-down the block indicated on the address pins. (See Section 11.1)

98

CFI Query

This command puts the device into the CFI-Query mode so that reading the device will output

Common Flash Interface information. See Section 10.1.3 and Appendix C, “Common Flash

C0

Protection

Program

Set-Up

This is a two-cycle command. The first cycle prepares the CUI for a program operation to the

protection register. The second cycle latches addresses and data information and initiates the

WSM to execute the Protection Program algorithm to the protection register. The flash outputs

Status Register data when CE# or OE# is toggled. A Read Array command is required after

programming to read array data. See Section 11.5.

10

Alt. Prog Set-Up

Operates the same as Program Set-up command. (See 0x40/Program Set-Up)

00

Invalid/

Reserved

Unassigned commands should not be used. Intel reserves the right to redefine these codes for

future functions.

Note:

See Appendix A, “Write State Machine States” for mode transition information.

相关PDF资料 |

PDF描述 |

|---|---|

| RC4194K | DUAL OUTPUT, ADJUSTABLE MIXED REGULATOR, MBFM9 |

| RM4194K | DUAL OUTPUT, ADJUSTABLE MIXED REGULATOR, MBFM9 |

| RC4194D | DUAL OUTPUT, ADJUSTABLE MIXED REGULATOR, CDIP14 |

| RM4194D/883B | DUAL OUTPUT, ADJUSTABLE MIXED REGULATOR, CDIP14 |

| RM4194D | DUAL OUTPUT, ADJUSTABLE MIXED REGULATOR, CDIP14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RC28F160C3BD70A | 功能描述:IC FLASH 16MBIT 70NS 64BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:96 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:16M(2M x 8,1M x 16) 速度:70ns 接口:并联 电源电压:2.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 |

| RC28F160C3TA110 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:Advanced+ Boot Block Flash Memory (C3) |

| RC28F160C3TA70 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:Advanced+ Boot Block Flash Memory (C3) |

| RC28F160C3TA90 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:Advanced+ Boot Block Flash Memory (C3) |

| RC28F160C3TA90SB93 | 功能描述:IC FLASH 16MBIT 90NS 64BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。