- 您现在的位置:买卖IC网 > PDF目录192292 > S19237PB13 (APPLIEDMICRO INC) TRANSCEIVER, PBGA255 PDF资料下载

参数资料

| 型号: | S19237PB13 |

| 厂商: | APPLIEDMICRO INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | TRANSCEIVER, PBGA255 |

| 封装: | PLASTIC, BGA-255 |

| 文件页数: | 25/60页 |

| 文件大小: | 1418K |

| 代理商: | S19237PB13 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

S19237 – SONET STS-192/10GbE CMOS Transceiver

with ISI Compensation

AMCC Confidential and Proprietary

DS1454

31

Data Sheet

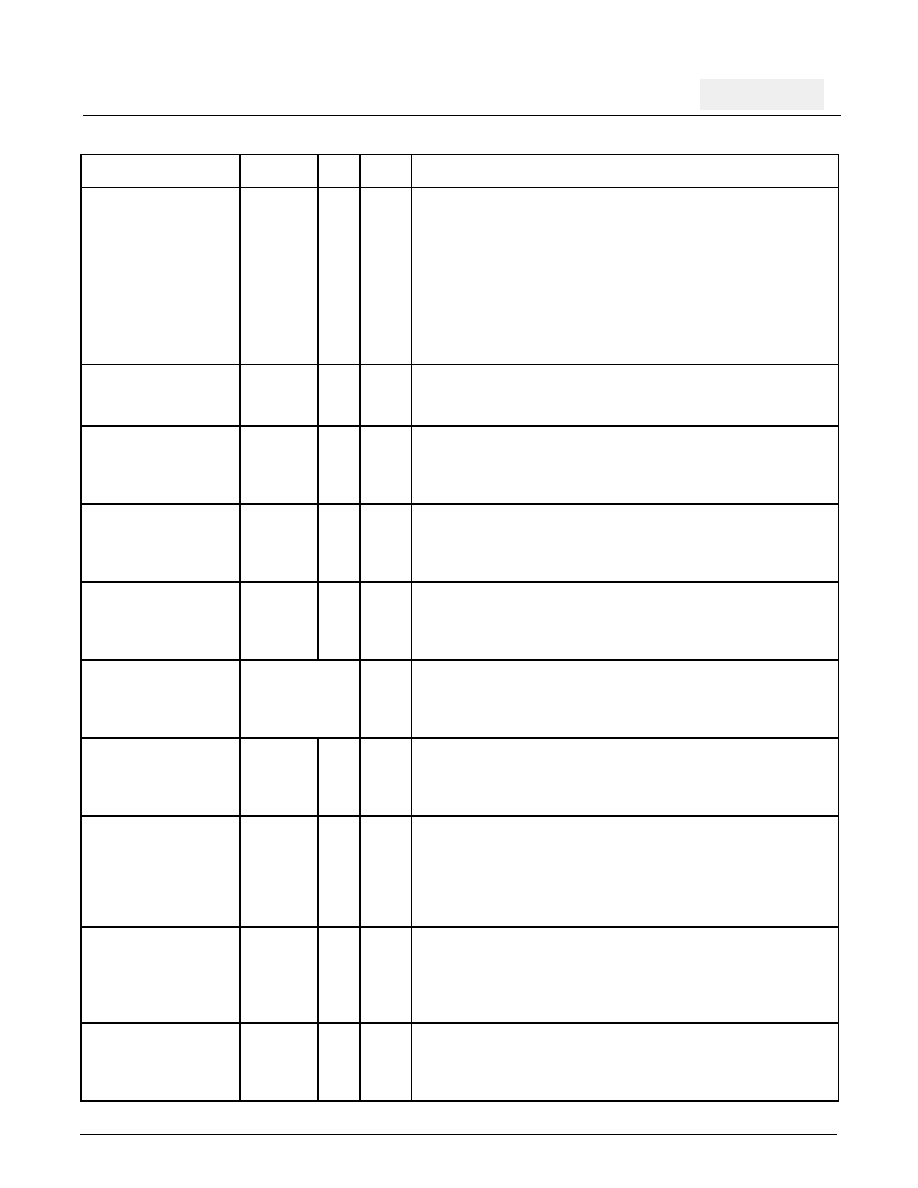

PAOFFADJ9

PAOFFADJ8

PAOFFADJ7

PAOFFADJ6

PAOFFADJ5

PAOFFADJ4

PAOFFADJ3

PAOFFADJ2

PAOFFADJ1

PAOFFADJ0

MDIO

I

Post-Amp Offset Adjust. Used to correct duty cycle distortion on

the input data signal. See Table 6 for details. This signal can be

accessed through the MDIO bus register. The default state will

depend up on the fuse settings and may vary from one device to

another.

ADAPOFFADJ

MDIO

I

Adaptive Post-Amp Offset Adjust Enable. Enables the adaptive

offset adjustment control. See Table 7 for details. This signal can be

accessed through the MDIO bus register (Default = 1).

PAEQUADJ2

PAEQUADJ1

PAEQUADJ0

MDIO

I

Post-Amp Equalization Adjust (ISI Compensation Control). Used

to adjust input serial data equalization control. This signal compen-

sates for the ISI. See Table 8 for details. This signal can be accessed

through the MDIO bus register (Default = 0,0,0).

PHASE_ADJ2

PHASE_ADJ1

PHASE_ADJ0

MDIO

I

Phase Adjust. Used to adjust the phase between the recovered

clock and data. The phase adjust can improve the bit error rate and

link budget. See Table 5 for details. This signal can be accessed

through the MDIO bus register (Default = 0,0,0).

CRU_REFCLKP

CRU_REFCLKN

REFCLK

Diff CML

I

T4

T3

Receive Reference Clock. 155.52 MHz (or equivalent FEC/10

Gigabit Ethernet frequency) input used as the reference for the inter-

nal bit clock frequency synthesizer. This input is internally biased and

terminated. This input must be AC coupled.

RXCAP1

RXCAP2

Analog

P6

P7

Receive Loop Filter Capacitors. Connections for external loop filter

capacitors and resistors. See Figure 22, External Loop Filter Compo-

Components.

LCKREFN

MDIO

I

Lock to Reference. Active low. When active, the PLL is forced to

lock to the local reference clock input (CRU_REFCLK). If unused,

connect to logic ‘1’ for normal operation. This signal can be accessed

through MDIO bus register (Default = 1).

SDLVCMOS

LVCMOS

Pull Up

I

M7

Signal Detect. An LVCMOS single-ended input to be driven by the

external optical receiver module to indicate a loss of received optical

power. When a loss-of-light condition occurs, the internal PLL will be

forced to lock to the CRU_REFCLK input signal. The POUTP/N will

be forced to a logic ‘0’ state when SDLVCMOS is inactive. The active

level of this input may be programmed by SD_POL.

SD_POL

MDIO

I

Signal Detect Polarity. This signal will set the SDLVCMOS input as

either active high or active low. Setting this pin low will set the

SDLVCMOS input as active low. Setting this pin high will set the

SDLVCMOS input as active high. This signal can be accessed

through the MDIO bus register (Default = 1).

KILLPOUTB

MDIO

I

Kill Parallel Data Output. Active low. For normal operation,

KILLPOUTB is high. When this input is low, it will force the

POUT[15:0] output to a logic ‘0’ state. This signal can be accessed

through the MDIO bus register (Default = 1).

Table 17. Input Pin Assignments and Descriptions (Continued)

Pin Name

Level

I/O

Pin#

Description

相关PDF资料 |

PDF描述 |

|---|---|

| S1950E-FREQ-OUT25 | CRYSTAL OSCILLATOR, CLOCK, 80 MHz - 125 MHz, ACMOS OUTPUT |

| S1F78100Y2A0 | 6 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2B0 | 5 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2C0 | 3.2 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2F0 | 2.2 V FIXED POSITIVE REGULATOR, PSSO3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S19237PB13-2 | 制造商:AppliedMicro 功能描述: |

| S19237PBICC | 制造商:AppliedMicro 功能描述:IC INTERFACE TRANSCEIVER LOW POWER CMOS 255 BGA 制造商:AMCC 功能描述: |

| S19238CBI | 制造商:AppliedMicro 功能描述: |

| S19250 | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:STS-192 SONET/SDH/FEC/GbE/FC 16-bit Transceiver with EDC |

| S19250PBIC | 制造商:AppliedMicro 功能描述:10G SERDES EDC/SFI-4 |

发布紧急采购,3分钟左右您将得到回复。