- 您现在的位置:买卖IC网 > PDF目录192292 > S19237PB13 (APPLIEDMICRO INC) TRANSCEIVER, PBGA255 PDF资料下载

参数资料

| 型号: | S19237PB13 |

| 厂商: | APPLIEDMICRO INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | TRANSCEIVER, PBGA255 |

| 封装: | PLASTIC, BGA-255 |

| 文件页数: | 3/60页 |

| 文件大小: | 1418K |

| 代理商: | S19237PB13 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

S19237 – SONET STS-192/10GbE CMOS Transceiver

with ISI Compensation

AMCC Confidential and Proprietary

DS1454

11

Data Sheet

TSD Output Amplitude Adjust (TSDAMPADJ) –

MDIO Register

The TSD Output Amplitude Adjust (TSDAMPADJ)

inputs are used to select Transmit Serial Output data

(TSD) voltage swing levels. The low swing option will

save about 30 mW of power and is compatible with the

XFI electrical specification (for applications with the

XFP module). See Table 3, TSD Output Amplitude

Adjust. This input is only accessible through the MDIO

bus register.

The BOLD CELLS denote the default state

Automatic FIFO Initialization (AUTO_FIFO_INIT) –

MDIO Register

This active high control input internally connects the

transmit FIFO signals (PHERR output and PHINIT

input) and automatically initializes the FIFO in case of

a PCLK/PICLK set-up or hold time violation. When

active, the PHERR output and PHINIT input do not

have to be shorted through the MDIO bus. This input is

only accessible through the MDIO bus register.

Transmit Built-In Self Test Enable (TX_BIST_EN) –

MDIO Register

This active high input enables the transmit built-in self

tes t mode. For normal system operation,

TX_BIST_EN should be programmed to logic low. The

S19237 goes in the BIST mode when TX_BIST_EN is

programmed to logic high. Once the TX_BIST_EN is

programmed to logic high, the PRBS generator will

start sending the PRBS/user defined pattern (see

Table 11 for details). The checker will be activated but

will not start checking for the valid data pattern until

RX_LOCKDET is active. This input is only accessible

through the MDIO bus register.

Transmit Built-In Self Test Clear (TX_BIST_CLR) –

MDIO Register

This active high level sensitive input clears the trans-

mit built-in self test error (TX_BIST_ERR). For normal

system operation, TX_BIST_CLR should be pro-

grammed to logic low. The TX_BIST_ERR flag can be

cleared by asserting the TX_BIST_CLR in the BIST

m ode o r by res e ttin g ( R STB) th e S192 37 .

TX_BIST_CLR is an active high level sensitive input.

In or der for th e t r ansmit checker to clear the

TX_BIST_ERR flag, TX_BIST_CLR must be asserted

high. This input is only accessible through the MDIO

bus register.

TRANSMIT OUTPUT PIN DESCRIPTION

Transmit Serial Data (TSDP/N) – External Pin

The differential High Speed CML Transmit Serial Data

(TSDP/N) output is the serialized version of the incom-

ing parallel data stream. This output is typically used to

drive the laser driver.

Parallel Clock (PCLKP/N) – External Pin

The LVDS Parallel Clock (PCLKP/N) output is a

622.08 MHz (or equivalent FEC/10 Gigabit Ethernet

rate) internally generated clock output used to coordi-

nate parallel data transfers with upstream logic. The

PCLKP/N is directly derived from the CSU_REFCLKP/

N in the normal operating mode. In SLPTIME mode,

the PCLK is derived from the internal receive serial

clock (RSCLK). PCLK is the divided-down version of

the internal TXCLK. PCLK is used to clock data out of

the upstream devices (framer/mapper). PCLK is also

used internally to clock data from the FIFO into the

parallel-to-serial shift register.

155.52 MHz Clock Output (TX_155MCKP/N) –

External Pin

The LVDS 155.52 MHz Clock Output (or equivalent

FEC/10 Gigabit Ethernet rate) TX_155MCKP/N pin is

an internally generated clock output used to drive the

reference clock input (CRU_REFCLKP/N) of the

receive section of the S19237 in the normal mode of

operation. The TX_155MCKP/N cannot be used as

the reference clock (CRU_REFCLKP/N) for the

receive section of the S19237 in the RLPTIME or SLP-

TIME mode.

Transmit Lock Detect (TX_LOCKDET) – MDIO Reg-

ister and External Pin

The active high transmit Lock Detect is an LVCMOS

output. This asynchronous output will be active high

once the internal PLL has locked to the clock provided

on the CSU_REFCLK input. The TX_LOCKDET out-

put goes active (high) when the PCLK is within 500

ppm from the CSU_REFCLK. This output can be

accessed through the MDIO bus register and through

an external LVCMOS pin.

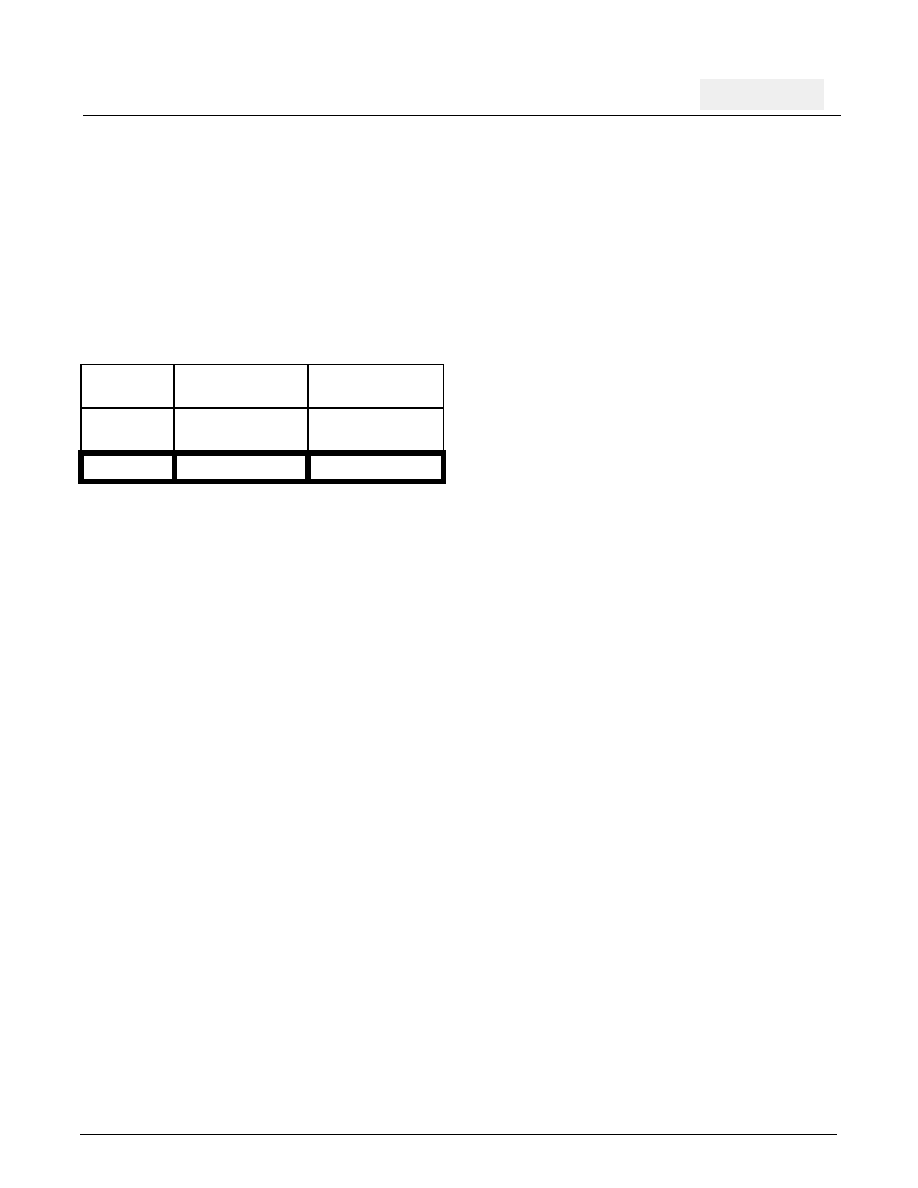

Table 3. TSD Output Amplitude Adjust

TSDAMPADJ

TSD Min Output

Single-Ended Swing

TSD Max Output

Single-Ended Swing

0 - XFP

Applications

180 mV

385 mV

1

400 mV

560 mV

相关PDF资料 |

PDF描述 |

|---|---|

| S1950E-FREQ-OUT25 | CRYSTAL OSCILLATOR, CLOCK, 80 MHz - 125 MHz, ACMOS OUTPUT |

| S1F78100Y2A0 | 6 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2B0 | 5 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2C0 | 3.2 V FIXED POSITIVE REGULATOR, PSSO3 |

| S1F78100Y2F0 | 2.2 V FIXED POSITIVE REGULATOR, PSSO3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S19237PB13-2 | 制造商:AppliedMicro 功能描述: |

| S19237PBICC | 制造商:AppliedMicro 功能描述:IC INTERFACE TRANSCEIVER LOW POWER CMOS 255 BGA 制造商:AMCC 功能描述: |

| S19238CBI | 制造商:AppliedMicro 功能描述: |

| S19250 | 制造商:AMCC 制造商全称:Applied Micro Circuits Corporation 功能描述:STS-192 SONET/SDH/FEC/GbE/FC 16-bit Transceiver with EDC |

| S19250PBIC | 制造商:AppliedMicro 功能描述:10G SERDES EDC/SFI-4 |

发布紧急采购,3分钟左右您将得到回复。