- 您现在的位置:买卖IC网 > Datasheet目录369 > W9725G6KB-25I (Winbond Electronics)IC DDR2 SDRAM 256MBIT 84WBGA Datasheet资料下载

参数资料

| 型号: | W9725G6KB-25I |

| 厂商: | Winbond Electronics |

| 文件页数: | 29/87页 |

| 文件大小: | 0K |

| 描述: | IC DDR2 SDRAM 256MBIT 84WBGA |

| 标准包装: | 209 |

| 格式 - 存储器: | RAM |

| 存储器类型: | DDR2 SDRAM |

| 存储容量: | 256M(16Mx16) |

| 速度: | 2.5ns |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | -40°C ~ 95°C |

| 封装/外壳: | 84-TFBGA |

| 供应商设备封装: | 84-WBGA(8x12.5) |

| 包装: | * |

| 其它名称: | Q7118748 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

�� �

�

�

�W9725G6KB�

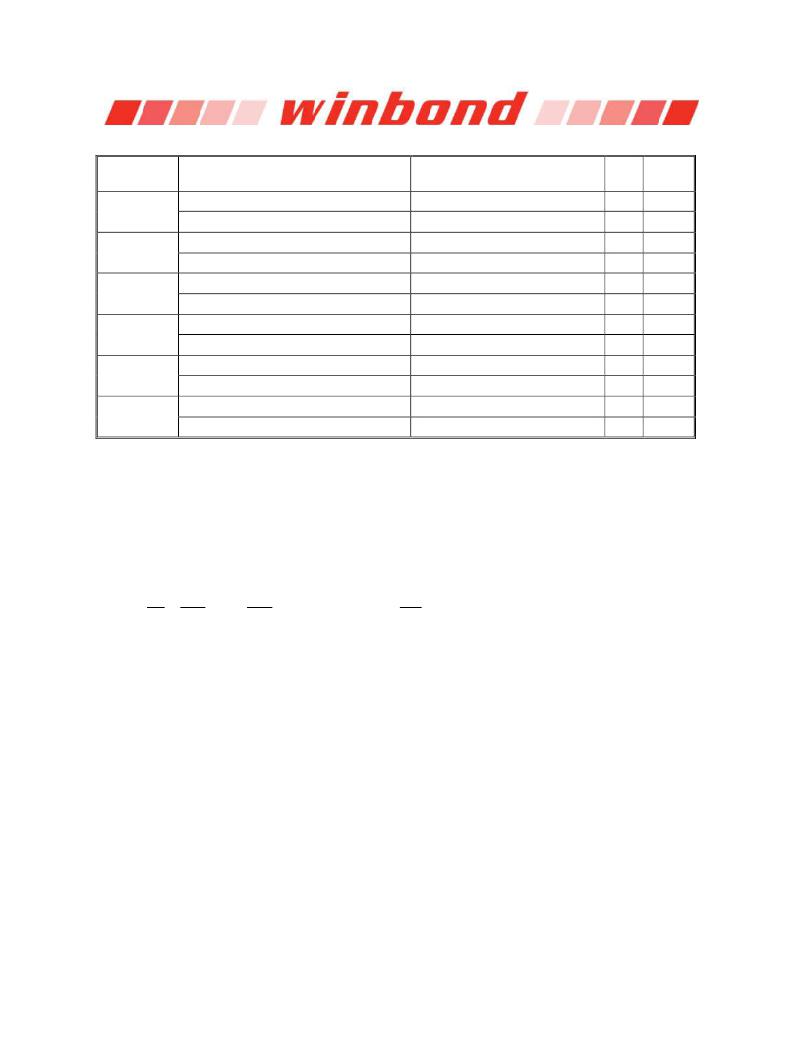

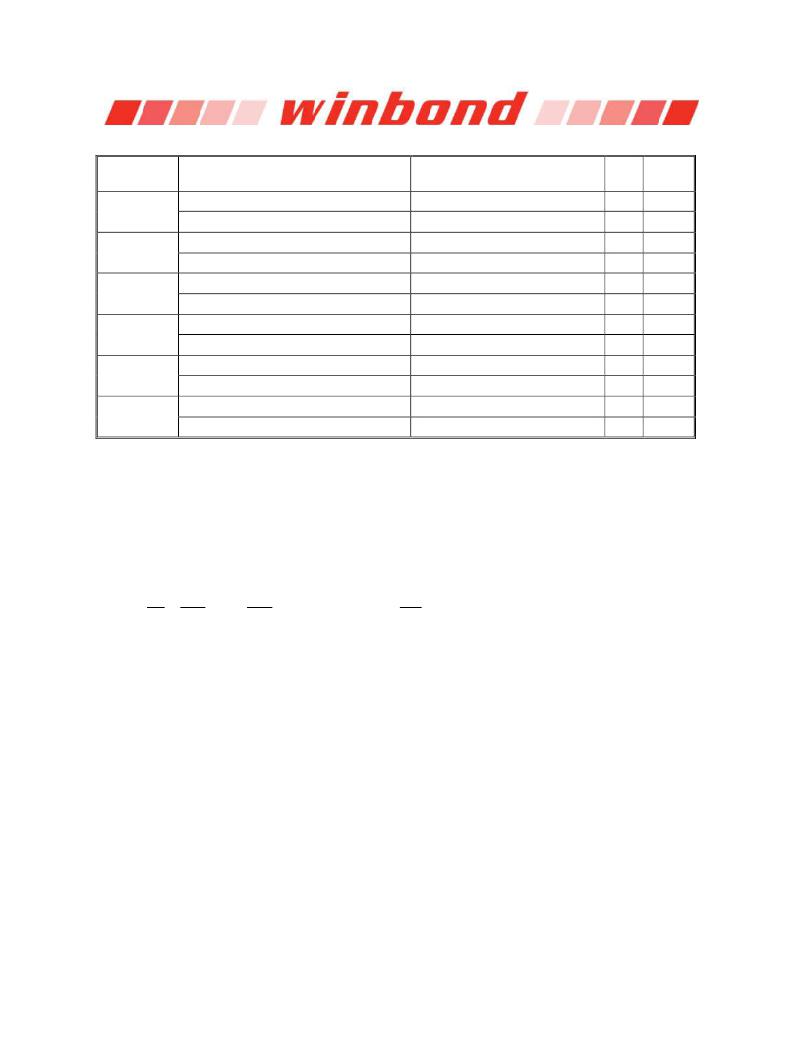

�Table� 5� –� Precharge� &� Auto-precharge� clarifications�

�From�

�To� Command�

�Minimum� Delay� between� “From�

�Unit�

�Notes�

�Command�

�Command”� to� “To� Command”�

�Read�

�Read� w/AP�

�Write�

�Write� w/AP�

�Precharge�

�Precharge�

�All�

�Precharge� (to� same� Bank� as� Read)�

�Precharge� All�

�Precharge (to same Bank as Read w/AP)�

�Precharge� All�

�Precharge� (to� same� Bank� as� Write)�

�Precharge� All�

�Precharge (to same Bank as Write w/AP)�

�Precharge� All�

�Precharge� (to� same� Bank� as� Precharge)�

�Precharge� All�

�Precharge�

�Precharge� All�

�AL� +� BL/2� +� max(RTP,� 2)� -� 2�

�AL� +� BL/2� +� max(RTP,� 2)� -� 2�

�AL� +� BL/2� +� max(RTP,� 2)� -� 2�

�AL� +� BL/2� +� max(RTP,� 2)� -� 2�

�WL� +� BL/2� +� t� WR�

�WL� +� BL/2� +� t� WR�

�WL� +� BL/2� +� WR�

�WL� +� BL/2� +� WR�

�1�

�1�

�1�

�1�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�clks�

�1,� 2�

�1,� 2�

�1,� 2�

�1,� 2�

�2�

�2�

�2�

�2�

�2�

�2�

�2�

�2�

�Notes:�

�1.� RTP[cycles]� =� RU{� tRTP[nS]� /� tCK(avg)[nS]� },� where� RU� stands� for� round� up.�

�2.� For� a� given� bank,� the� precharge� period� should� be� counted� from� the� latest� precharge� command,� either� one� bank� precharge� or�

�precharge� all,� issued� to� that� bank.� The� precharge� period� is� satisfied� after� tRP� depending� on� the� latest� precharge� command�

�issued� to� that� bank.�

�8.8�

�Refresh� Operation�

�DDR2� SDRAM� requires� a� refresh� of� all� rows� in� any� rolling� 64� mS� interval.� The� necessary� refresh� can�

�be� generated� in� one� of� two� ways:� by� explicit� Auto� Refresh� commands� or� by� an� internally� timed� Self�

�Refresh� mode.� Dividing� the� number� of� device� rows� into� the� rolling� 64� mS� interval� defines� the� average�

�refresh� interval,� t� REFI� ,� which� is� a� guideline� to� controllers� for� distributed� refresh� timing.�

�When� CS� ,� RAS� and� CAS� are� held� LOW� and� WE� HIGH� at� the� rising� edge� of� the� clock,� the� chip�

�enters� the� Refresh� mode� (REF).� All� banks� of� the� DDR2� SDRAM� must� be� precharged� and� idle� for� a�

�minimum� of� the� Precharge� time� (t� RP� )� before� the� Refresh� command� (REF)� can� be� applied.� An� address�

�counter,� internal� to� the� device,� supplies� the� bank� address� during� the� refresh� cycle.� No� control� of� the�

�external� address� bus� is� required� once� this� cycle� has� started.� (Example� timing� waveform� refer� to� 11.28�

�Self� Refresh� diagram� in� Chapter� 11)�

�8.9�

�Power� Down� Mode�

�Power-down� is� synchronously� entered� when� CKE� is� registered� LOW,� along� with� NOP� or� Deselect�

�command.� CKE� is� not� allowed� to� go� LOW� while� mode� register� or� extended� mode� register� command�

�time,� or� read� or� write� operation� is� in� progress.� CKE� is� allowed� to� go� LOW� while� any� other� operation�

�such� as� row� activation,� Precharge� or� Auto-precharge� or� Auto� Refresh� is� in� progress,� but� power� down�

�I� DD� specification� will� not� be� applied� until� finishing� those� operations.�

�The� DLL� should� be� in� a� locked� state� when� power-down� is� entered.� Otherwise� DLL� should� be� reset�

�after� exiting� power-down� mode� for� proper� read� operation.�

�Publication� Release� Date:� Sep.� 03,� 2012�

�-� 29� -�

�Revision� A03�

�相关PDF资料 |

PDF描述 |

|---|---|

| W972GG6JB-3I | IC DDR2 SDRAM 2GBITS 84WBGA |

| W9751G6IB-25 | IC DDR2-800 SDRAM 512MB 84-WBGA |

| W9751G6KB-25 | IC DDR2 SDRAM 512MBIT 84WBGA |

| W9812G6JH-6I | IC SDRAM 128MBIT 54TSOPII |

| W9816G6IH-6I | IC SDRAM 16MBIT 50TSOPII |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G6KB25I TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X16, IND TEMP |

| W9725G6KB25K | 制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask |

| W9725G6KB-3 | 制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask |

| W9725G8JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 8 BIT DDR2 SDRAM |

| W9725G8JB25 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 32Mx8 1.8V 60-Pin WBGA |

发布紧急采购,3分钟左右您将得到回复。