- 您现在的位置:买卖IC网 > Datasheet目录369 > W9725G6KB-25I (Winbond Electronics)IC DDR2 SDRAM 256MBIT 84WBGA Datasheet资料下载

参数资料

| 型号: | W9725G6KB-25I |

| 厂商: | Winbond Electronics |

| 文件页数: | 43/87页 |

| 文件大小: | 0K |

| 描述: | IC DDR2 SDRAM 256MBIT 84WBGA |

| 标准包装: | 209 |

| 格式 - 存储器: | RAM |

| 存储器类型: | DDR2 SDRAM |

| 存储容量: | 256M(16Mx16) |

| 速度: | 2.5ns |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | -40°C ~ 95°C |

| 封装/外壳: | 84-TFBGA |

| 供应商设备封装: | 84-WBGA(8x12.5) |

| 包装: | * |

| 其它名称: | Q7118748 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

�� �

�

�

�W9725G6KB�

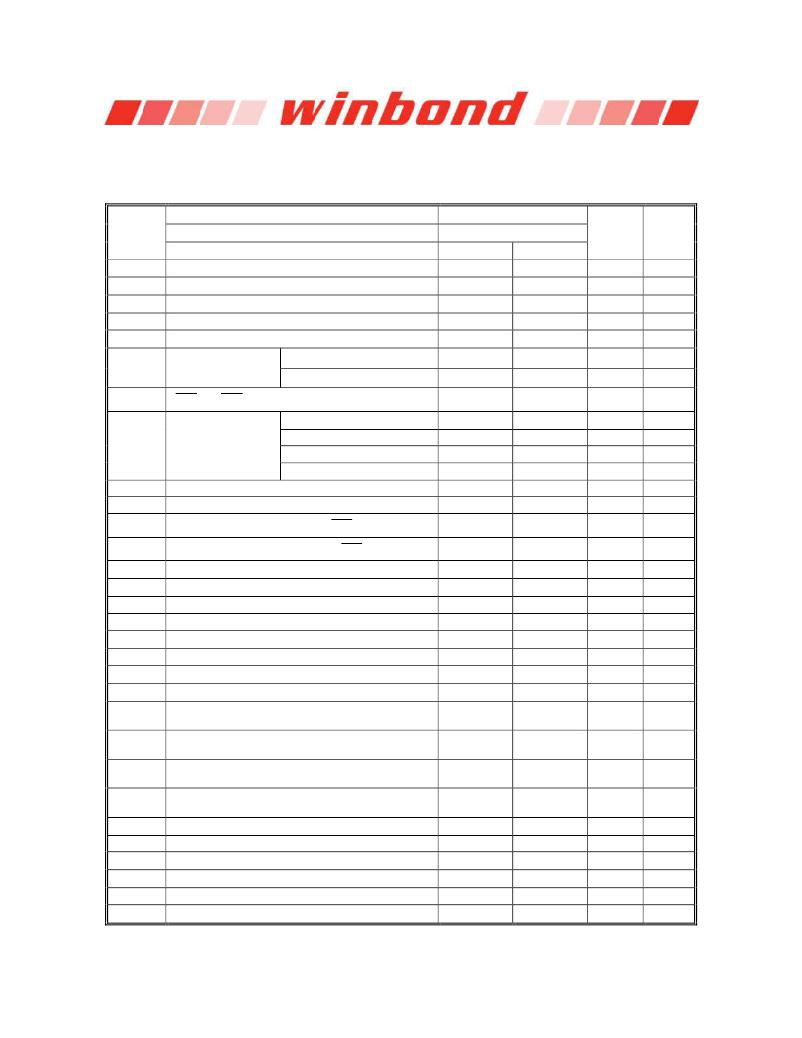

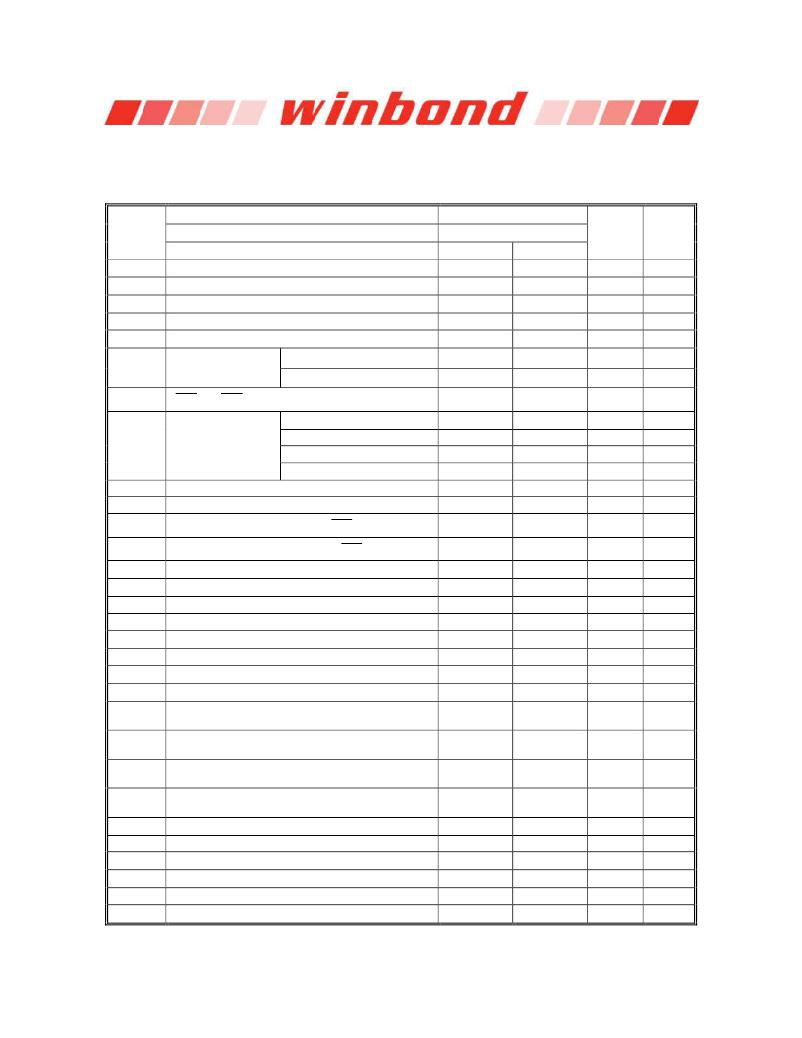

�10.11� AC� Characteristics�

�10.11.1� AC� Characteristics� and� Operating� Condition� for� -18� speed� grade�

�Notes:� 1-3� and� 45-47� apply� to� the� entire� table�

�SPEED� GRADE�

�DDR2-1066� (-18)�

�SYM.�

�Bin(CL-t� RCD� -t� RP)�

�PARAMETER�

�MIN.�

�7-7-7�

�MAX.�

�UNIT� 25�

�NOTES�

�t� RCD�

�t� RP�

�t� RC�

�t� RAS�

�t� RFC�

�Active� to� Read/Write� Command� Delay� Time�

�Precharge� to� Active� Command� Period�

�Active� to� Ref/Active� Command� Period�

�Active� to� Precharge� Command� Period�

�Auto� Refresh� to� Active/Auto� Refresh� command� period�

�13.125�

�13.125�

�58.125�

�45�

�75�

�?�

�?�

�?�

�70000�

�?�

�nS�

�nS�

�nS�

�nS�

�nS�

�23�

�23�

�23�

�4,23�

�5�

�t� REFI�

�Average� periodic�

�refresh� Interval�

�0°C� ≤� T� CASE� ≤� 85°C�

�85°C� <� T� CASE� ≤� 95°C�

�?�

�?�

�7.8�

�3.9�

�μ� S�

�μ� S�

�5�

�5,6�

�t� CCD�

�CAS� to� CAS� command� delay�

�2�

�?�

�n� CK�

�t� CK(avg)� @� CL=4�

�3.75�

�7.5�

�nS�

�30,31�

�t� CK(avg)�

�Average� clock� period�

�t� CK(avg)� @� CL=5�

�t� CK(avg)� @� CL=6�

�t� CK(avg)� @� CL=7�

�3�

�2.5�

�1.875�

�7.5�

�7.5�

�7.5�

�nS�

�nS�

�nS�

�30,31�

�30,31�

�30,31�

�t� CH(avg)�

�t� CL(avg)�

�t� AC�

�t� DQSCK�

�t� DQSQ�

�t� CKE�

�t� RRD�

�t� FAW�

�t� WR�

�t� DAL�

�t� WTR�

�t� RTP�

�t� IS� (base)�

�t� IH� (base)�

�t� IS� (ref)�

�t� IH� (ref)�

�t� IPW�

�t� DQSS�

�t� DSS�

�t� DSH�

�t� DQSH�

�t� DQSL�

�Average� clock� high� pulse� width�

�Average� clock� low� pulse� width�

�DQ� output� access� time� from� CLK/� CLK�

�DQS� output� access� time� from� CLK� /� CLK�

�DQS-DQ� skew� for� DQS� &� associated� DQ� signals�

�CKE� minimum� high� and� low� pulse� width�

�Active� to� active� command� period� for� 1KB� page� size�

�Four� Activate� Window� for� 1KB� page� size�

�Write� recovery� time�

�Auto-precharge� write� recovery� +� precharge� time�

�Internal� Write� to� Read� command� delay�

�Internal� Read� to� Precharge� command� delay�

�Address� and� control� input� setup� time�

�Address� and� control� input� hold� time�

�Address� and� control� input� setup� time�

�Address� and� control� input� hold� time�

�Address� and� control� input� pulse� width� for� each� input�

�DQS latching rising transitions to associated clock edges�

�DQS� falling� edge� to� CLK� setup� time�

�DQS� falling� edge� hold� time� from� CLK�

�DQS� input� high� pulse� width�

�DQS� input� low� pulse� width�

�0.48�

�0.48�

�-350�

�-325�

�?�

�3�

�7.5�

�35�

�15�

�WR� +� tn� RP�

�7.5�

�7.5�

�125�

�200�

�325�

�325�

�0.6�

�-0.25�

�0.2�

�0.2�

�0.35�

�0.35�

�0.52�

�0.52�

�350�

�325�

�175�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�0.25�

�?�

�?�

�?�

�?�

�t� CK(avg)�

�t� CK(avg)�

�pS�

�pS�

�pS�

�n� CK�

�nS�

�nS�

�nS�

�n� CK�

�nS�

�nS�

�pS�

�pS�

�pS�

�pS�

�t� CK(avg)�

�t� CK(avg)�

�t� CK(avg)�

�t� CK(avg)�

�t� CK(avg)�

�t� CK(avg)�

�30,31�

�30,31�

�35�

�35�

�13�

�7�

�8,23�

�23�

�23�

�24�

�9,23�

�4,23�

�10,26,�

�40,42,43�

�11,26,�

�40,42,43�

�10,26,�

�40,42,43�

�11,26,�

�40,42,43�

�28�

�28�

�28�

�Publication� Release� Date:� Sep.� 03,� 2012�

�-� 43� -�

�Revision� A03�

�相关PDF资料 |

PDF描述 |

|---|---|

| W972GG6JB-3I | IC DDR2 SDRAM 2GBITS 84WBGA |

| W9751G6IB-25 | IC DDR2-800 SDRAM 512MB 84-WBGA |

| W9751G6KB-25 | IC DDR2 SDRAM 512MBIT 84WBGA |

| W9812G6JH-6I | IC SDRAM 128MBIT 54TSOPII |

| W9816G6IH-6I | IC SDRAM 16MBIT 50TSOPII |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G6KB25I TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X16, IND TEMP |

| W9725G6KB25K | 制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask |

| W9725G6KB-3 | 制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask |

| W9725G8JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 8 BIT DDR2 SDRAM |

| W9725G8JB25 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 32Mx8 1.8V 60-Pin WBGA |

发布紧急采购,3分钟左右您将得到回复。