- 您现在的位置:买卖IC网 > PDF目录17091 > EK-V6-ML630-G-J (Xilinx Inc)VIRTEX-6 HXT FPGA ML630 EVAL KIT PDF资料下载

参数资料

| 型号: | EK-V6-ML630-G-J |

| 厂商: | Xilinx Inc |

| 文件页数: | 41/65页 |

| 文件大小: | 0K |

| 描述: | VIRTEX-6 HXT FPGA ML630 EVAL KIT |

| 标准包装: | 1 |

| 系列: | Virtex® 6 HXT |

| 类型: | FPGA |

| 适用于相关产品: | Virtex?-6 XC6VHX565T |

| 所含物品: | 板,线缆,软件和文档 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

�� �

�

�

�Virtex-6� FPGA� Data� Sheet:� DC� and� Switching� Characteristics�

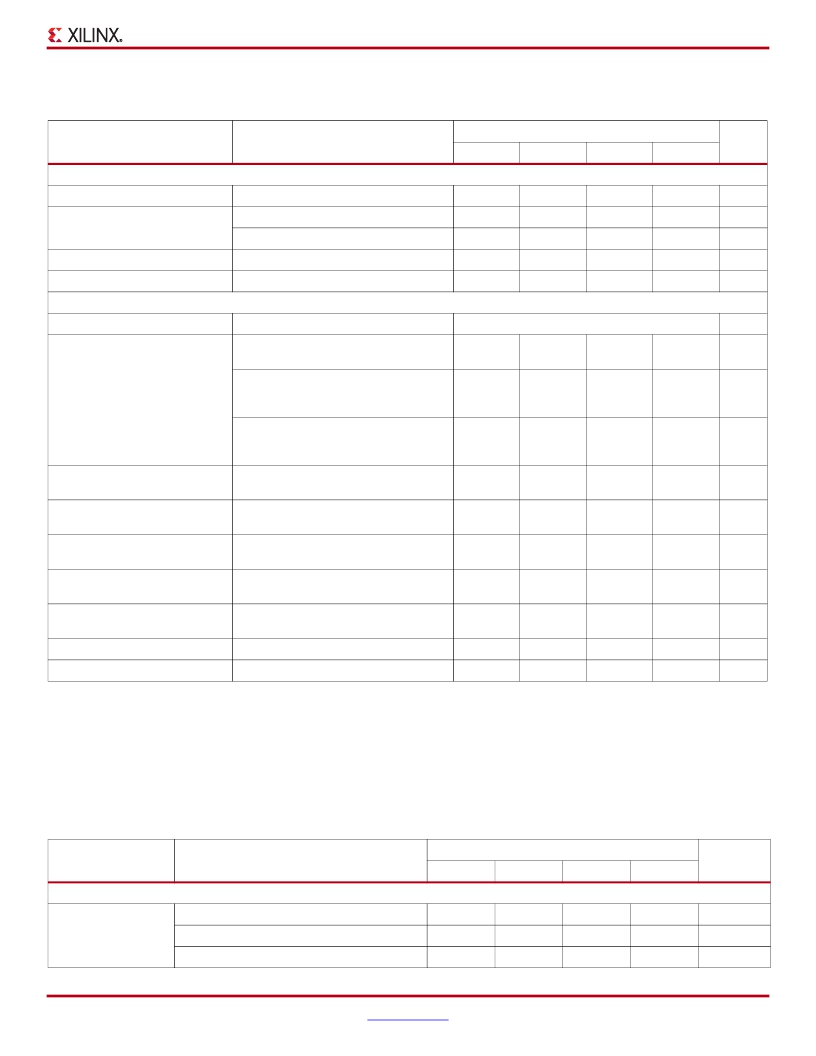

�Input/Output� Delay� Switching� Characteristics�

�Table� 53:� Input/Output� Delay� Switching� Characteristics�

�Symbol�

�Description�

�-3�

�Speed� Grade�

�-2� -1�

�-1L�

�Units�

�IDELAYCTRL�

�T� DLYCCO_RDY�

�Reset� to� Ready� for� IDELAYCTRL�

�3.00�

�3.00�

�3.00�

�3.25�

�μs�

�F� IDELAYCTRL_REF�

�REFCLK� frequency� =�

�REFCLK� frequency� =�

�200.0� (1)�

�300.0� (1)�

�200�

�300�

�200�

�300�

�200�

�–�

�200�

�–�

�MHz�

�MHz�

�IDELAYCTRL_REF_PRECISION�

�T� IDELAYCTRL_RPW�

�REFCLK� precision�

�Minimum� Reset� pulse� width�

�±10�

�50.00�

�±10�

�50.00�

�±10�

�50.00�

�±10�

�52.50�

�MHz�

�ns�

�IODELAY�

�T� IDELAYRESOLUTION�

�IODELAY� Chain� Delay� Resolution�

�1/(32� x� 2� x� F� REF� )�

�ps�

�Pattern� dependent� period� jitter� in� delay�

�0�

�0�

�0�

�0�

�ps�

�chain� for� clock� pattern.� (2)�

�per� tap�

�Pattern� dependent� period� jitter� in� delay�

�±5�

�±5�

�±5�

�±5�

�ps�

�T� IDELAYPAT_JIT�

�chain� for� random� data� pattern�

�(PRBS� 23).� (3)�

�per� tap�

�Pattern� dependent� period� jitter� in� delay�

�±9�

�±9�

�±9�

�±9�

�ps�

�chain� for� random� data� pattern�

�(PRBS� 23).� (4)�

�per� tap�

�T� IODELAY_CLK_MAX�

�T� IODCCK_CE� /� T� IODCKC_CE�

�T� IODCK_INC� /� T� IODCKC_INC�

�T� IODCCK_RST� /� T� IODCKC_RST�

�T� IODDO_T�

�T� IODDO_IDATAIN�

�T� IODDO_ODATAIN�

�Maximum� frequency� of� CLK� input� to�

�IODELAY�

�CE� pin� Setup/Hold� with� respect� to� CK�

�INC� pin� Setup/Hold� with� respect� to� CK�

�RST� pin� Setup/Hold� with� respect� to� CK�

�TSCONTROL� delay� to� MUXE/MUXF�

�switching� and� through� IODELAY�

�Propagation� delay� through� IODELAY�

�Propagation� delay� through� IODELAY�

�500.00�

�0.45/�

�–0.09�

�0.23/�

�–0.02�

�0.57/�

�–0.08�

����420.00�

�0.53/�

�–0.09�

�0.27/�

�–0.01�

�0.62/�

�–0.08�

����300.00�

�0.65/�

�–0.09�

�0.31/�

�0.00�

�0.69/�

�–0.08�

����300.00�

�0.84/�

�–0.14�

�0.27/�

�–0.04�

�0.74/�

�–0.13�

����MHz�

�ns�

�ns�

�ns�

�ps�

�ps�

�ps�

�Notes:�

�1.�

�2.�

�3.�

�4.�

�5.�

�Average� Tap� Delay� at� 200� MHz� =� 78� ps,� at� 300� MHz� =� 52� ps.�

�When� HIGH_PERFORMANCE� mode� is� set� to� TRUE� or� FALSE.�

�When� HIGH_PERFORMANCE� mode� is� set� to� TRUE�

�When� HIGH_PERFORMANCE� mode� is� set� to� FALSE.�

�Delay� depends� on� IODELAY� tap� setting.� See� TRACE� report� for� actual� values.�

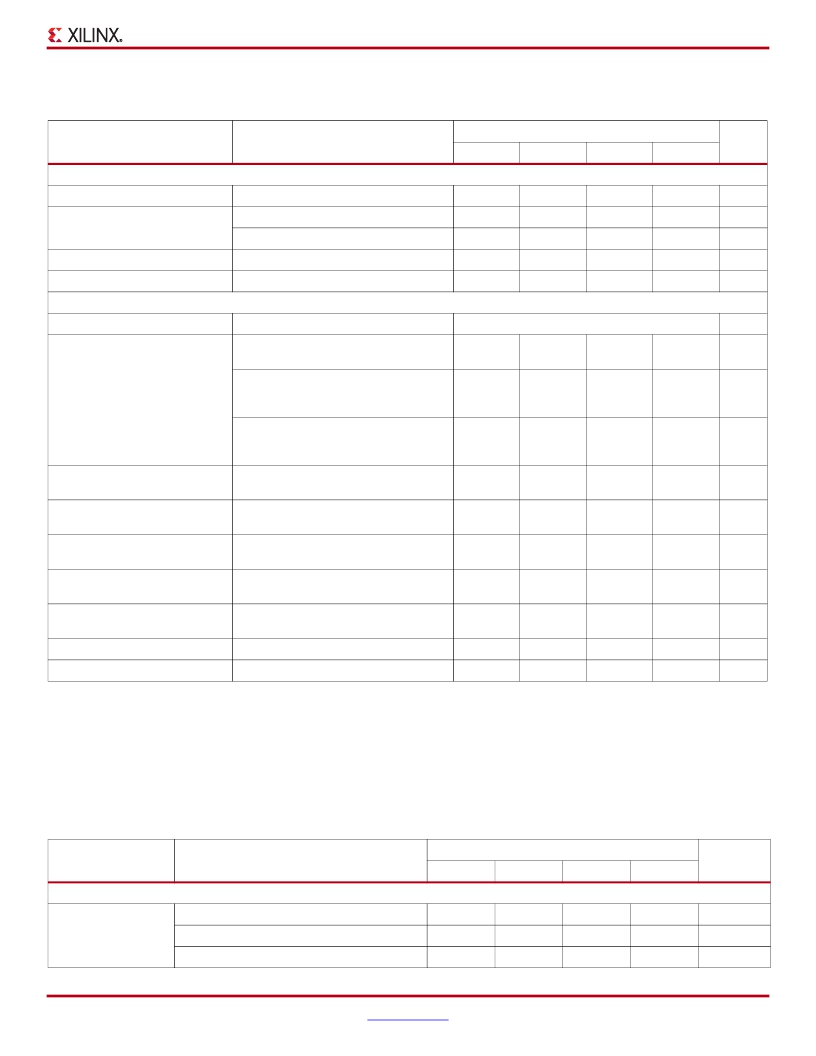

�CLB� Switching� Characteristics�

�Table� 54:� CLB� Switching� Characteristics�

�Symbol�

�Description�

�-3�

�Speed� Grade�

�-2� -1�

�-1L�

�Units�

�Combinatorial� Delays�

�T� ILO�

�An� –� Dn� LUT� address� to� A�

�An� –� Dn� LUT� address� to� AMUX/CMUX�

�An� –� Dn� LUT� address� to� BMUX_A�

�0.06�

�0.18�

�0.28�

�0.07�

�0.20�

�0.31�

�0.07�

�0.22�

�0.36�

�0.09�

�0.25�

�0.40�

�ns,� Max�

�ns,� Max�

�ns,� Max�

�DS152� (v3.6)� March� 18,� 2014�

�Product� Specification�

��41�

�相关PDF资料 |

PDF描述 |

|---|---|

| C8051F020-TB | BOARD PROTOTYPING W/C8051F020 |

| SDR-T2 | SCOTCH CODE REFILL T2 |

| CK-V6-ML628-G-J | KIT VIRTEX-6 CHAR ML628 JAPAN |

| CK-V6-ML623-G | BOARD DEV V6 WITH TX |

| CK-V6-ML623-G-J | BOARD DEV V6 WITH TX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EK-V6-ML631-G | 功能描述:VIRTEX-6 HXT FPGA ML631 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® 6 HXT 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V6-ML631-G-J | 功能描述:VIRTEX-6 HXT FPGA ML631 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® 6 HXT 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-CES-G | 功能描述:VIRTEX-7 VC707 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-CES-G-J | 功能描述:VIRTEX-7 VC707 EVAL KIT JAPAN RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-G | 制造商:Xilinx 功能描述:VIRTEX-7 FPGA VC707 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 制造商:Xilinx 功能描述:VIRTEX-7 VC707 FPGA EVAL KIT |

发布紧急采购,3分钟左右您将得到回复。