- 您现在的位置:买卖IC网 > PDF目录17091 > EK-V6-ML630-G-J (Xilinx Inc)VIRTEX-6 HXT FPGA ML630 EVAL KIT PDF资料下载

参数资料

| 型号: | EK-V6-ML630-G-J |

| 厂商: | Xilinx Inc |

| 文件页数: | 50/65页 |

| 文件大小: | 0K |

| 描述: | VIRTEX-6 HXT FPGA ML630 EVAL KIT |

| 标准包装: | 1 |

| 系列: | Virtex® 6 HXT |

| 类型: | FPGA |

| 适用于相关产品: | Virtex?-6 XC6VHX565T |

| 所含物品: | 板,线缆,软件和文档 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

�� �

�

�

�Virtex-6� FPGA� Data� Sheet:� DC� and� Switching� Characteristics�

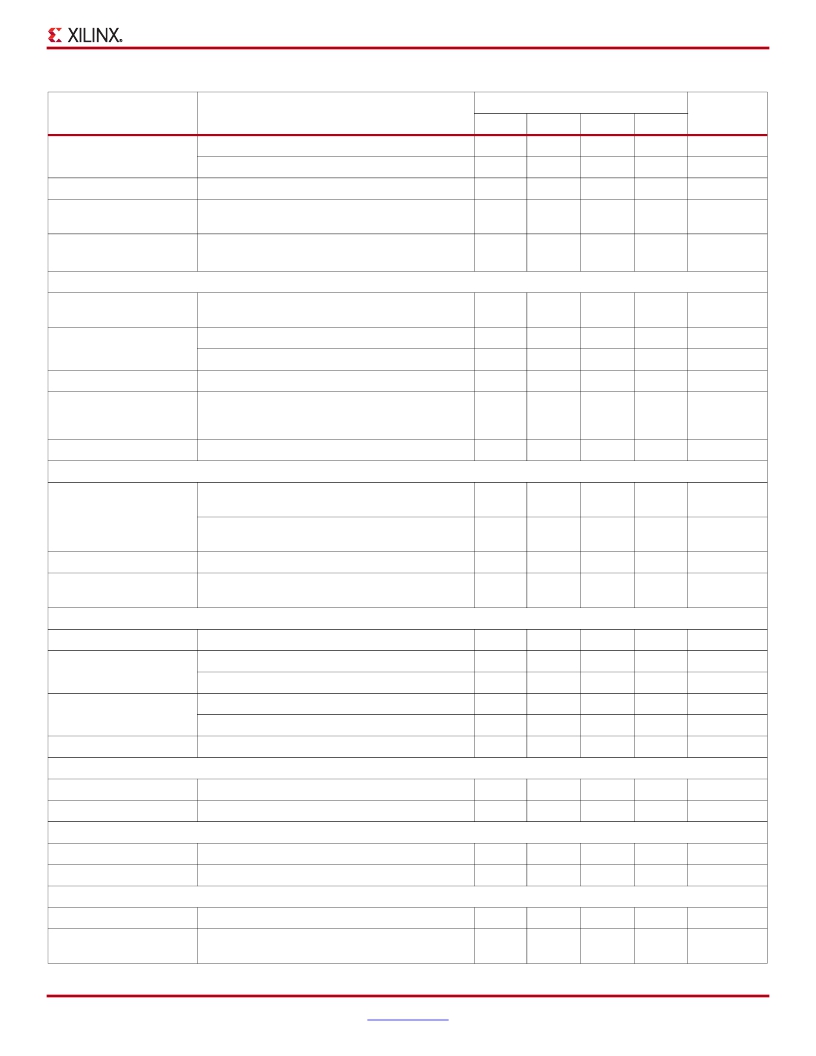

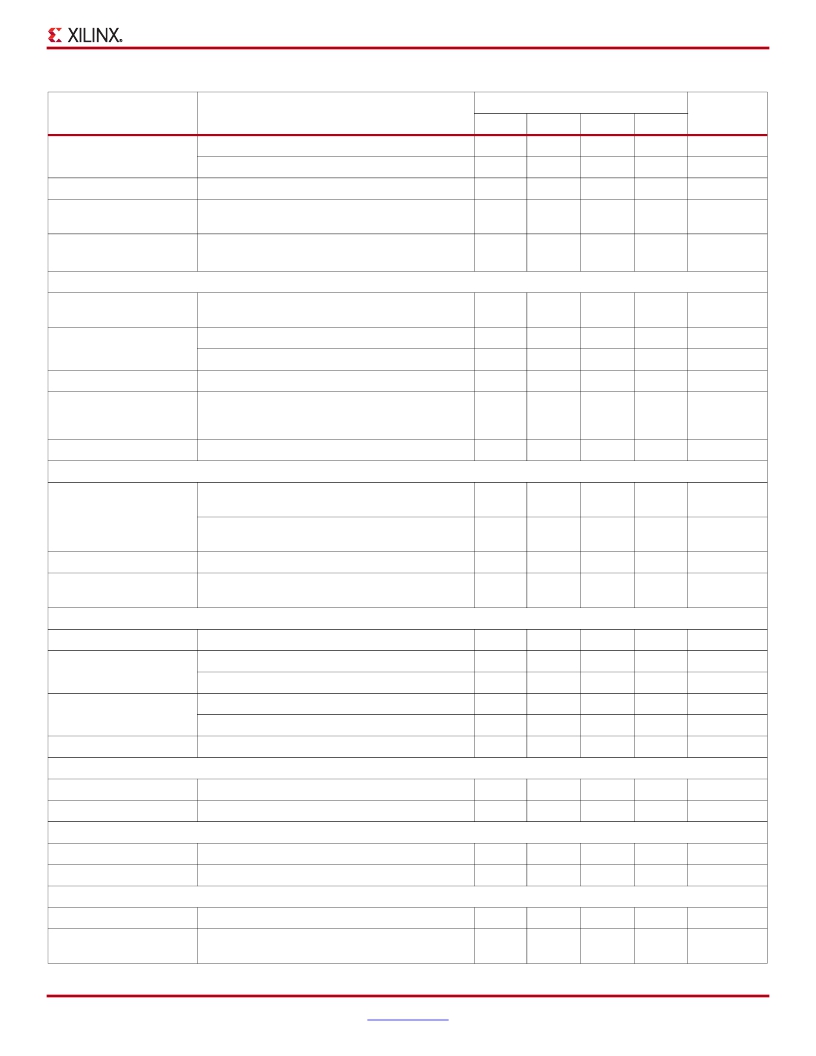

�Table� 59:� Configuration� Switching� Characteristics� (Cont’d)�

�Symbol�

�Description�

�-3�

�Speed� Grade�

�-2� -1�

�-1L�

�Units�

�T� SMCKBY�

�F� SMCCK�

�F� RBCCK�

�F� MCCKTOL�

�CCLK� to� BUSY� out� in� readback� at� 2.5V�

�CCLK� to� BUSY� out� in� readback� at� 1.8V�

�Maximum� Frequency� with� respect� to� nominal� CCLK�

�Maximum� Readback� Frequency� with� respect� to�

�nominal� CCLK�

�Frequency� tolerance,� master� mode� with�

�6�

�6�

�100�

�100�

�55�

�6�

�6�

�100�

�100�

�55�

�6�

�6�

�100�

�100�

�55�

�7�

�7�

�70�

�60�

�60�

�ns,� Max�

�ns,� Max�

�MHz,� Max�

�MHz,� Max�

�%�

�respect� to� nominal� CCLK�

�Boundary-Scan� Port� Timing� Specifications�

�T� TAPTCK� /T� TCKTAP�

�T� TCKTDO�

�F� TCK�

�F� TCKB_MIN�

�TMS� and� TDI� Setup� time� before� TCK/� Hold� time�

�after� TCK�

�TCK� falling� edge� to� TDO� output� valid� at� 2.5V�

�TCK� falling� edge� to� TDO� output� valid� at� 1.8V�

�Maximum� configuration� TCK� clock� frequency�

�Minimum� boundary-scan� TCK� clock� frequency�

�when� using� IEEE� Std� 1149.6� (AC-JTAG).� Minimum�

�3.0/2.0�

�6�

�6�

�66�

�15�

�3.0/2.0�

�6�

�6�

�66�

�15�

�3.0/2.0�

�6�

�6�

�66�

�15�

�4.0/2.0�

�7�

�7�

�33�

�15�

�ns,� Min�

�ns,� Max�

�ns,� Max�

�MHz,� Max�

�MHz,� Min�

�operating� temperature� for� IEEE� Std� 1149.6� is� 0°C.�

�F� TCKB�

�Maximum� boundary-scan� TCK� clock� frequency�

�66�

�66�

�66�

�33�

�MHz,� Max�

�BPI� Master� Flash� Mode� Programming� Switching�

�T� BPICCO� (2)�

�ADDR[25:0],� RS[1:0],� FCS_B,� FOE_B,� FWE_B�

�outputs� valid� after� CCLK� rising� edge� at� 2.5V�

�ADDR[25:0],� RS[1:0],� FCS_B,� FOE_B,� FWE_B�

�6�

�6�

�6�

�6�

�6�

�6�

�7�

�7�

�ns�

�ns�

�outputs� valid� after� CCLK� rising� edge� at� 1.8V�

�T� BPIDCC� /T� BPICCD�

�T� INITADDR�

�Setup/Hold� on� D[15:0]� data� input� pins�

�Minimum� period� of� initial� ADDR[25:0]� address�

�cycles�

�4.0/0.0�

�3�

�4.0/0.0�

�3�

�4.0/0.0�

�3�

�5.0/0.0�

�3�

�ns�

�CCLK� cycles�

�SPI� Master� Flash� Mode� Programming� Switching�

�T� SPIDCC� /T� SPIDCCD�

�T� SPICCM�

�T� SPICCFC�

�T� FSINIT� /T� FSINITH�

�DIN� Setup/Hold� before/after� the� rising� CCLK� edge�

�MOSI� clock� to� out� at� 2.5V�

�MOSI� clock� to� out� at� 1.8V�

�FCS_B� clock� to� out� at� 2.5V�

�FCS_B� clock� to� out� at� 1.8V�

�FS[2:0]� to� INIT_B� rising� edge� Setup� and� Hold�

�3.0/0.0�

�6�

�6�

�6�

�6�

�2�

�3.0/0.0�

�6�

�6�

�6�

�6�

�2�

�3.0/0.0�

�6�

�6�

�6�

�6�

�2�

�3.5/0.0�

�7�

�7�

�7�

�7�

�2�

�ns�

�ns�

�ns�

�ns�

�ns�

�μs�

�CCLK� Output� (Master� Modes)�

�T� MCCKL�

�T� MCCKH�

�Master� CCLK� clock� Low� time� duty� cycle�

�Master� CCLK� clock� High� time� duty� cycle�

�45/55�

�45/55�

�45/55�

�45/55�

�45/55�

�45/55�

�40/60�

�40/60�

�%,� Min/Max�

�%,� Min/Max�

�CCLK� Input� (Slave� Modes)�

�T� SCCKL�

�T� SCCKH�

�Slave� CCLK� clock� minimum� Low� time�

�Slave� CCLK� clock� minimum� High� time�

�2.5�

�2.5�

�2.5�

�2.5�

�2.5�

�2.5�

�2.5�

�2.5�

�ns,� Min�

�ns,� Min�

�Dynamic� Reconfiguration� Port� (DRP)� for� MMCM� Before� and� After� DCLK�

�F� DCK�

�T� MMCMDCK_DADDR� /�

�T� MMCMCKD_DADDR�

�Maximum� frequency� for� DCLK�

�DADDR� Setup/Hold�

�200�

�1.25/�

�0.00�

�200�

�1.40/�

�0.00�

�200�

�1.63/�

�0.00�

�200�

�1.64/�

�0.00�

�MHz�

�ns�

�DS152� (v3.6)� March� 18,� 2014�

�Product� Specification�

��50�

�相关PDF资料 |

PDF描述 |

|---|---|

| C8051F020-TB | BOARD PROTOTYPING W/C8051F020 |

| SDR-T2 | SCOTCH CODE REFILL T2 |

| CK-V6-ML628-G-J | KIT VIRTEX-6 CHAR ML628 JAPAN |

| CK-V6-ML623-G | BOARD DEV V6 WITH TX |

| CK-V6-ML623-G-J | BOARD DEV V6 WITH TX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EK-V6-ML631-G | 功能描述:VIRTEX-6 HXT FPGA ML631 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® 6 HXT 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V6-ML631-G-J | 功能描述:VIRTEX-6 HXT FPGA ML631 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® 6 HXT 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-CES-G | 功能描述:VIRTEX-7 VC707 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-CES-G-J | 功能描述:VIRTEX-7 VC707 EVAL KIT JAPAN RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| EK-V7-VC707-G | 制造商:Xilinx 功能描述:VIRTEX-7 FPGA VC707 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 制造商:Xilinx 功能描述:VIRTEX-7 VC707 FPGA EVAL KIT |

发布紧急采购,3分钟左右您将得到回复。