- 您现在的位置:买卖IC网 > PDF目录67684 > IBM37RGB524CF17A 1600 X 1280 PIXELS PALETTE-DAC DSPL CTLR, PQFP144 PDF资料下载

参数资料

| 型号: | IBM37RGB524CF17A |

| 元件分类: | 显示控制器 |

| 英文描述: | 1600 X 1280 PIXELS PALETTE-DAC DSPL CTLR, PQFP144 |

| 封装: | QFP-144 |

| 文件页数: | 4/72页 |

| 文件大小: | 509K |

| 代理商: | IBM37RGB524CF17A |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

6

March 17, 1995

RGB524

IBM

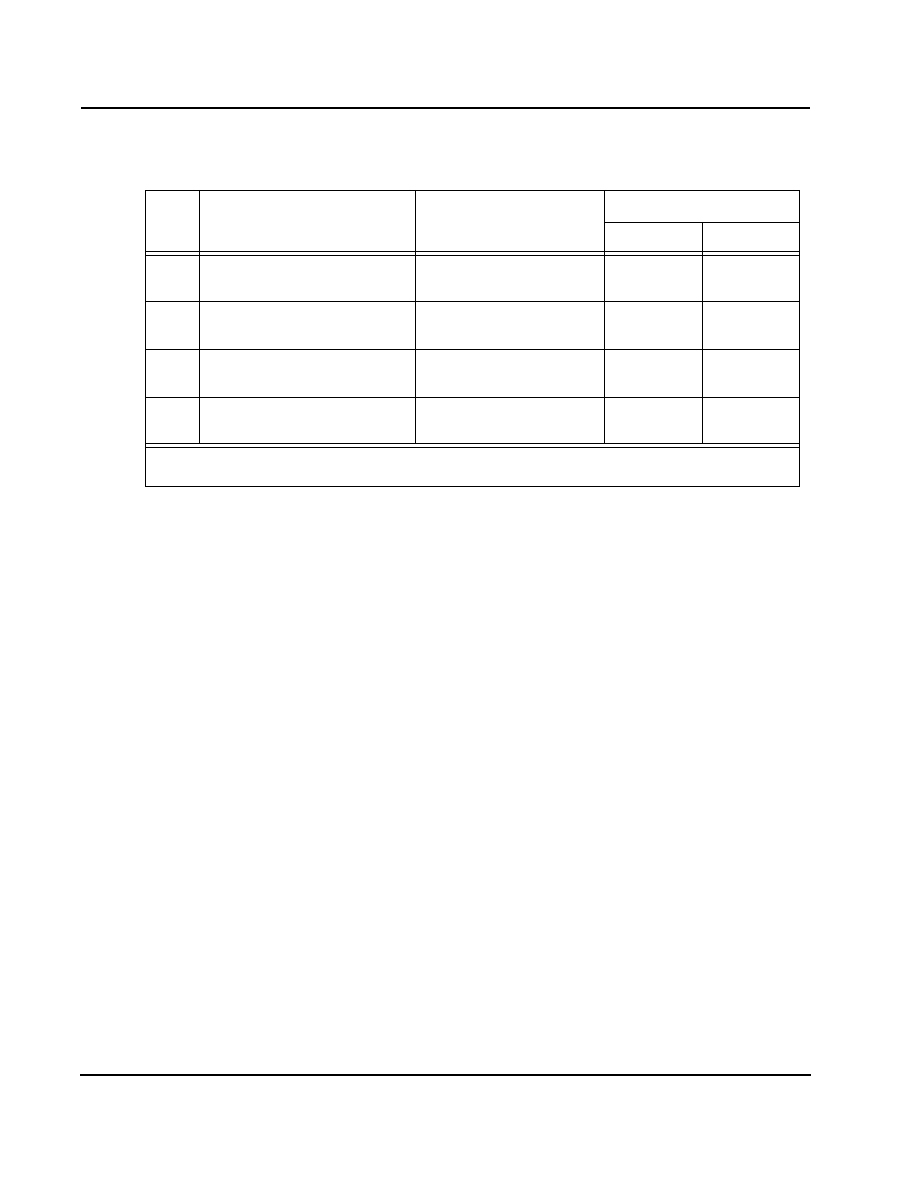

Table 3. PLL Equations

DF

Output Frequency

Internal VRF

Max Output Freq. (MHz)

170

220

00

FREF

× (VCO DIV COUNT + 65)

(REF DIV COUNT)

× 8

FREF

(REF DIV COUNT)

× 2

42.5

55.0

01

FREF

× (VCO DIV COUNT + 65)

(REF DIV COUNT)

× 4

FREF

(REF DIV COUNT)

× 2

85

110 (*)

10

FREF

× (VCO DIV COUNT + 65)

(REF DIV COUNT)

× 2

FREF

(REF DIV COUNT)

× 2

170 (*)

220 (*)

11

FREF

× (VCO DIV COUNT + 65)

REF DIV COUNT

FREF

REF DIV COUNT

170 (*)

220 (*)

1. FREF = REFCLK frequency

2. Frequencies marked with (*) are maximum pixel PLL frequencies. The SYSCLK PLL maximum output frequency is 100 MHz.

2.8

PLL Programming

The two PLLs are programmed identically. Three values

are used:

REF DIV COUNT (Reference Divide Count) This

number provides a count value for dividing

down the incoming REFCLK. It must be

between 2 and 31. Operation of the PLL is

indeterminate if this number is 0 or 1.

VCO DIV COUNT (VCO Divide Count) This

number provides a count value for the divider

in the PLL feedback loop. The value can range

from 0 through 63. Internally, 65 is added to

VCO DIV COUNT, so that the PLL feedback

divider value ranges from 65 through 128.

DF (Desired Frequency) These are two bits with

values of 00, 01, 10, and 11. The intent of these

bits is to divide the operation of the PLL into

four frequency ranges. Following the divide of

the REFCLK provided by the REF DIV COUNT

there is an additional divide-by-two which is

selected or bypassed with the DF bits. Also, the

output of the PLL has a divider stage, or

postscaler, that is controlled by the DF bits.

Table 3, "PLL Equations," gives the general formulas for

programming the PLLs. Because of the action of the DF

bits there are four equations, one for each DF bit setting.

It is possible to program the PLLs with values that gen-

erate illegal operating conditions:

1.

The reference frequency VRF (Video Reference

Frequency), which is internal to the PLL, cannot be

less than 1 MHz.

2.

The internal VCO (Voltage Controlled Oscillator)

cannot exceed the rated speed of the product

(170/220 MHz).

3.

The SYSCLK output driven by the SYSCLK PLL

cannot exceed 100 MHz.

4.

The DDOTCLK output driven by the pixel PLL

cannot exceed 100 MHz.

Table 3, "PLL Equations," gives the equations for calcu-

lating the internal VRF. Table 3 also gives the maximum

allowable output frequency for each setting of DF. This

reects the action of the VCO postscaler. If the PLLs are

programmed so that these maximum dot clock frequen-

cies are not exceeded then the maximum VCO frequency

will not be exceeded.

相关PDF资料 |

PDF描述 |

|---|---|

| IC-WT-SO16N | ROTARY/LINEAR OPTICAL POSITION ENCODER |

| ICD2028SCR-5 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO20 |

| ICD2063SC-1 | 135 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICD2063SC-2 | 135 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICD2063SC-3 | 135 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM37RGB524CF22A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Video DAC with Color Palette (RAMDAC) |

| IBM39ENV422DLL00C | 制造商:IBM 功能描述: |

| IBM39ENV422PBA17C | 制造商:IBM Microelectronics 功能描述:VID ENCODER 420PIN HPBGA - Trays 制造商:IBM 功能描述:IBM IBM39ENV422PBA17C Encoders - Decoders |

| IBM39MPEGCD20PFD22C | 制造商:IBM 功能描述: |

| IBM39MPEGCS22PFJ22C | 制造商:IBM 功能描述: |

发布紧急采购,3分钟左右您将得到回复。