参数资料

| 型号: | W25Q64FVSSIG |

| 厂商: | Winbond Electronics |

| 文件页数: | 41/89页 |

| 文件大小: | 0K |

| 描述: | IC SPI FLASH 64MBIT 8SOIC |

| 标准包装: | 90 |

| 系列: | SpiFlash® |

| 格式 - 存储器: | 闪存 |

| 存储器类型: | FLASH |

| 存储容量: | 64M(8M x 8) |

| 速度: | 80MHz |

| 接口: | SPI 串行 |

| 电源电压: | 2.7 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

�� �

�

�

�W25Q64FV�

�6.2.18�

�Octal� Word� Read� Quad� I/O� (E3h)�

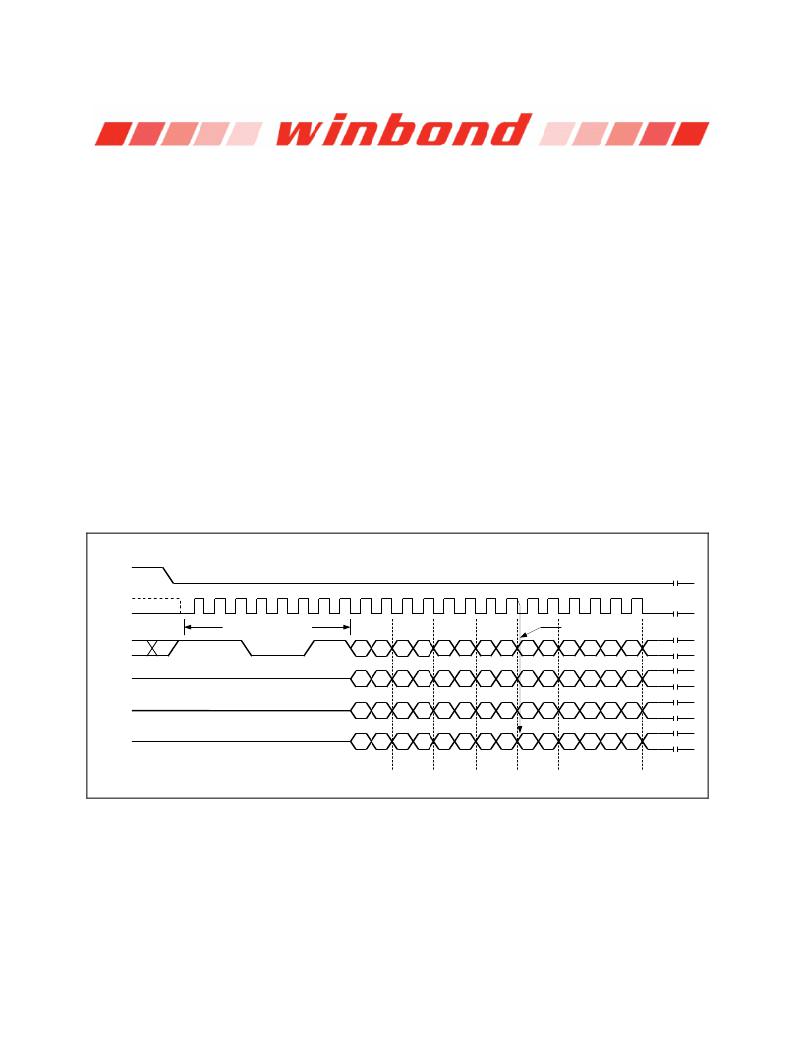

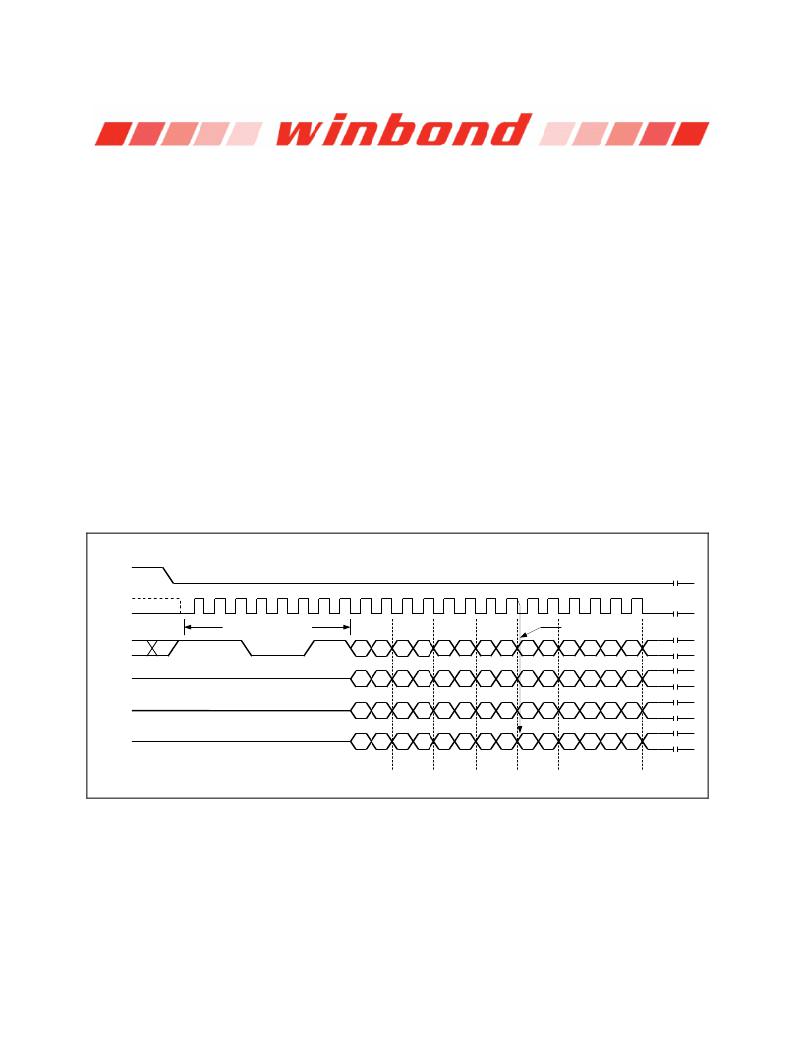

�The� Octal� Word� Read� Quad� I/O� (E3h)� instruction� is� similar� to� the� Fast� Read� Quad� I/O� (EBh)� instruction�

�except� that� the� lower� four� Address� bits� (A0,� A1,� A2,� A3)� must� equal� 0.� As� a� result,� the� dummy� clocks� are�

�not� required,� which� further� reduces� the� instruction� overhead� allowing� even� faster� random� access� for� code�

�execution� (XIP).� The� Quad� Enable� bit� (QE)� of� Status� Register-2� must� be� set� to� enable� the� Octal� Word�

�Read� Quad� I/O� Instruction.�

�Octal� Word� Read� Quad� I/O� with� “Continuous� Read� Mode”�

�The� Octal� Word� Read� Quad� I/O� instruction� can� further� reduce� instruction� overhead� through� setting� the�

�“Continuous� Read� Mode”� bits� (M7� -0)� after� the� input� Address� bits� (A23-0),� as� shown� in� Figure� 17a.� The�

�upper� nibble� of� the� (M7-4)� controls� the� length� of� the� next� Octal� Word� Read� Quad� I/O� instruction� through�

�the� inclusion� or� exclusion� of� the� first� byte� instruction� code.� The� lower� nibble� bits� of� the� (M3-� 0)� are� don’t�

�care� (“x”).� However,� the� IO� pins� should� be� high-impedance� prior� to� the� falling� edge� of� the� first� data� out�

�clock.�

�If� the� “Continuous� Read� Mode� ”� bits� M5-4� =� (1,0),� then� the� next� Fast� Read� Quad� I/O� instruction� (after� /CS�

�is� raised� and� then� lowered)� does� not� require� the� E3h� instruction� code,� as� shown� in� Figure� 17b.� This�

�reduces� the� instruction� sequence� by� eight� clocks� and� allows� the� Read� address� to� be� immediately� entered�

�after� /CS� is� asserted� low.� If� the� “Continuous� Read� Mode� ”� bits� M5-4� do� not� equal� to� (1,0),� the� next�

�instruction� (after� /CS� is� raised� and� then� lowered)� requires� the� first� byte� instruction� code,� thus� returning� to�

�normal� operation.� It� is� recommended� to� input� FFh� on� IO0� for� the� next� instruction� (8� clocks),� to� ensure� M4�

�=� 1� and� return� the� device� to� normal� operation.�

�/CS�

�Mode� 3�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�16�

�17�

�18�

�19�

�20�

�21�

�CLK�

�Mode� 0�

�Instruction� (E3h)�

�A23-16�

�A15-8�

�A7-0�

�M7-0�

�IOs� switch� from�

�Input� to� Output�

�IO� 0�

�IO� 1�

�IO� 2�

�IO� 3�

�20�

�21�

�22�

�23�

�16�

�17�

�18�

�19�

�12�

�13�

�14�

�15�

�8�

�9�

�10�

�11�

�4�

�5�

�6�

�7�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�Byte� 1�

�Byte� 2�

�Byte� 3�

�Byte� 4�

�Figure� 17a.� Octal� Word� Read� Quad� I/O� Instruction� (Initial� instruction� or� previous� M5-4� ?� 10,� SPI� Mode� only)�

�-� 41� -�

�Publication� Release� Date:�

�October� 07,� 2013�

�Revision� L�

�相关PDF资料 |

PDF描述 |

|---|---|

| EP1AGX35DF780I6 | IC ARRIA GX FPGA 35K 780FBGA |

| EP1AGX35DF780I6N | IC ARRIA GX FPGA 35K 780FBGA |

| EP4CE115F23C9L | IC CYCLONE IV FPGA 115K 484-FBGA |

| EP4CE115F23C8 | IC CYCLONE IV FPGA 115K 484-FBGA |

| A3PE3000L-1FG484 | IC FPGA 1KB FLASH 3M 484-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W25Q64FVSSIG TR | 制造商:Winbond Electronics Corp 功能描述:SPIFLASH, 64M-BIT, 4KB UNIFORM 制造商:Winbond Electronics Corp 功能描述:IC FLASH 64MBIT 104MHZ 8SOIC 制造商:Winbond 功能描述:SPIFLASH, 64M-BIT, 4KB UNIFORM |

| W25Q64FVSSIG/TRAY | 制造商:Winbond Electronics Corp 功能描述: |

| W25Q64FVSSIP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 64M-BIT SERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI |

| W25Q64FVTCIG | 制造商:Winbond Electronics Corp 功能描述:64MBIT SPI |

| W25Q64FVTCIP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 64M-BIT SERIAL FLASH MEMORY WITH DUAL/QUAD SPI & QPI |

发布紧急采购,3分钟左右您将得到回复。