- 您现在的位置:买卖IC网 > PDF目录1987 > AD9549ABCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9549ABCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9549A Mask Change 22/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750MHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 38 of 76

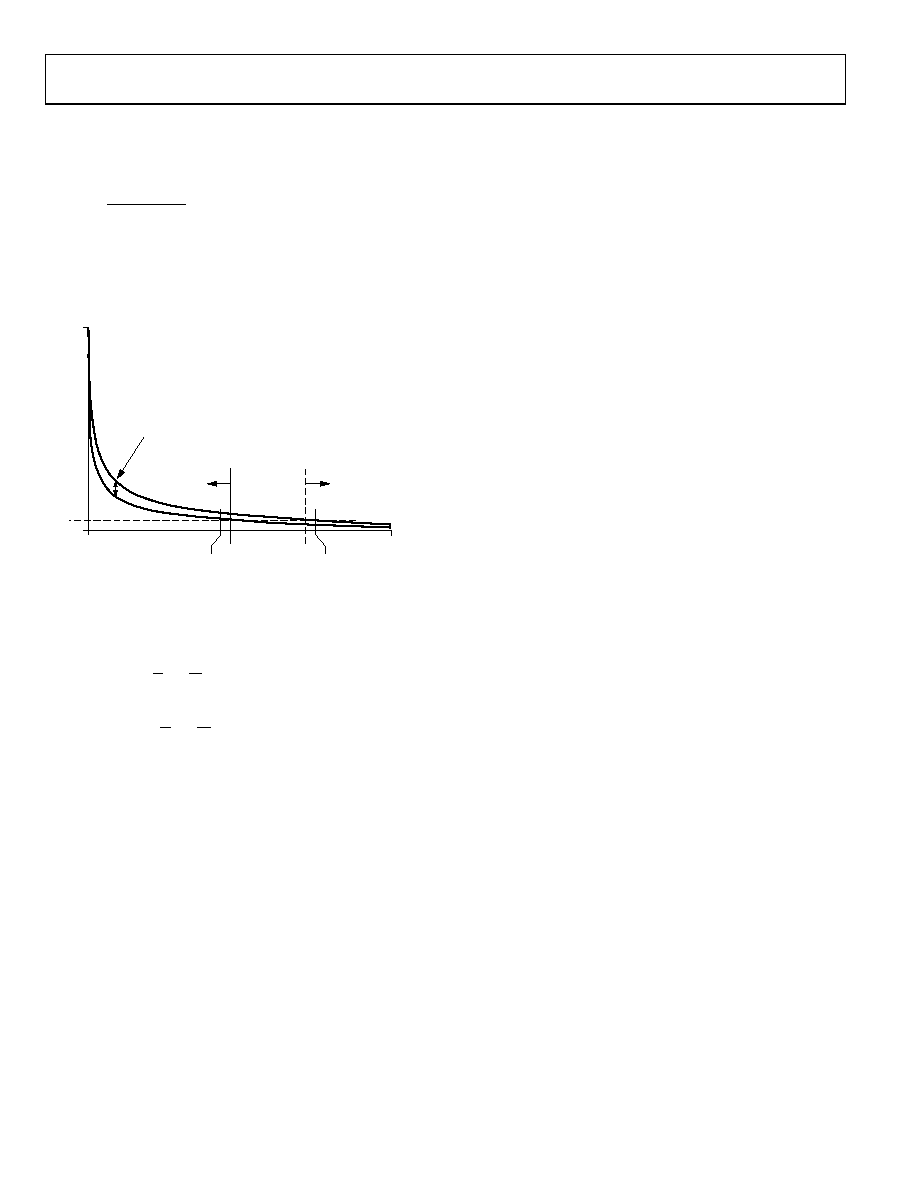

The measurement error (ε) associated with the frequency

estimator depends on the choice of the measurement interval

parameter (K). These are related by

( )

1

floor

=

ρK

ε

With a specified fractional error (ε0), only those values of K

for which ε ≤ ε0 results in a frequency estimate that meets the

requirements. A plot of ε vs. K (for a given ρ) takes on the

general form that is shown in Figure 48.

ε BOUNDED

BY ENVELOPE

ε

0

1

216

ε < ε

0 FOR

SOME K

(K0 < K < K1)

ε > ε

0 FOR

ALL K < K0

ε < ε

0 FOR

ALL K > K1

KLO

K0

KHI

K1

K

06744-

048

Figure 48. Frequency Estimator ε vs. K

An iterative technique is necessary to determine the exact values

of K0 and K1. However, a closed form exists for a conservative

estimate of K0 (KLOW) and K1 (KHIGH).

+

=

0

LOW

ε

ρ

K

1

ceil

+

=

0

HIGH

ε

ρ

K

1

2

ceil

As an example, consider the following system conditions:

fS = 400 MHz

R = 8

fREF_IN = 155.52 MHz

ε0 = 0.00005 (that is, 50 ppm)

These conditions yield KMAX = 3185, which is the largest K value

that can be programmed without causing the frequency estimator

counter to overflow. With K = KMAX, Tmeas = 163.84 μs, and ε =

30.2 ppm, KMAX generally (but not always) yields the smallest

value of ε, but this comes at the cost of the largest measurement

time (Tmeas).

If the measurement time must be reduced, then KHIGH can be used

instead of KMAX. This yields KHIGH = 1945, Tmeas = 100.05 μs, and

ε = 39.4 ppm.

The measurement time can be further reduced (though

marginally) by using K1 instead of KHIGH. K1 is found by solving

the ε ≤ ε0 inequality iteratively. To do so, start with K = KHIGH

and decrement K successively while evaluating the inequality

for each value of K. Stop the process the first time that the

inequality is no longer satisfied and add 1 to the value of K

thus obtained. The result is the value of K1. For the preceding

example, K1 = 1912, Tmeas = 98.35 μs, and ε = 39.8 ppm.

If a further reduction of the measurement time is necessary,

K0 can be used. K0 is found in a manner similar to K1. Start with

K = KLOW and increment K successively while evaluating the

inequality for each value of K. Stop the process the first time that

the inequality is satisfied. The result is the value of K0. For the

preceding example, K0 = 1005, Tmeas = 51.70 μs, and ε = 49.0 ppm.

If external frequency division exists between the DAC output

and the FDBK_IN pins, the frequency estimator should not be

used because it will calculate the wrong initial frequency.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

| AD9553BCPZ-REEL7 | IC INTEGER-N CLCK GEN 32LFCSP |

| AD9557BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 40LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

发布紧急采购,3分钟左右您将得到回复。