- 您现在的位置:买卖IC网 > PDF目录1987 > AD9549ABCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9549ABCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 35/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9549A Mask Change 22/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750MHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 40 of 76

The DDS output frequency listed in Table 8 assumes that

the internal DAC sampling frequency (fS) is 1 GHz. These

frequencies scale 1:1 with fS, meaning that other startup

frequencies are available by varying the SYSCLK frequency.

At startup, the internal frequency multiplier defaults to 40×

when the Xtal/PLL mode is selected via the status pins.

Note that when using this mode, the digital PLL loop is still open,

and the AD9549 is acting as a frequency synthesizer. The

frequency dividers and DPLL loop filter must still be

programmed before closing the loop.

Table 8. Default Power-Up Frequency Options for 1 GHz

System Clock

Status Pin

SYSCLK

Input Mode

Output Frequency

(MHz)

S4

S3

S2

S1

0

Xtal/PLL

0

1

Xtal /PLL

38.87939

0

1

0

Xtal /PLL

51.83411

0

1

Xtal /PLL

61.43188

0

1

0

Xtal /PLL

77.75879

0

1

0

1

Xtal /PLL

92.14783

0

1

0

Xtal /PLL

122.87903

0

1

Xtal /PLL

155.51758

1

0

Direct

0

1

0

1

Direct

38.87939

1

0

1

0

Direct

51.83411

1

0

1

Direct

61.43188

1

0

Direct

77.75879

1

0

1

Direct

92.14783

1

0

Direct

122.87903

1

Direct

155.51758

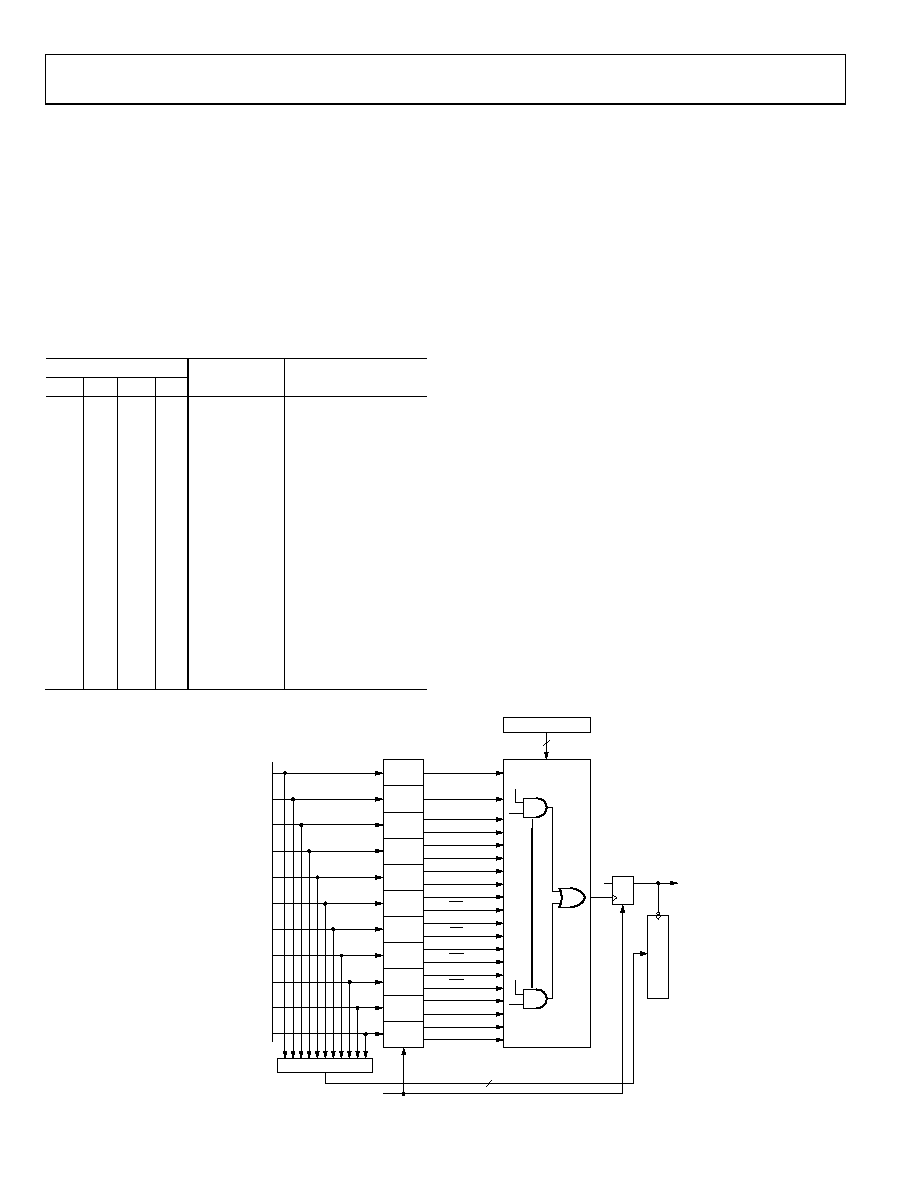

Interrupt Request (IRQ)

Any one of the four status pins (S1 to S4) can be programmed as

an IRQ pin. If a status pin is programmed as an IRQ pin, the state

of the internal IRQ flag appears on that pin. An IRQ flag is

internally generated based on the change of state of any one of

the internal status flags. The individual status flags are routed to

a read-only I/O register (status register) so that the user can

interrogate the status of any of these flags at any time. Furthermore,

each status flag is monitored for a change in state. In some cases,

only a change of state in one direction is necessary (for example, the

frequency estimate done flag), but in most cases, the status flags are

monitored for a change of state in either direction (see Figure 50).

Whether or not a particular state change is allowed to generate

an IRQ is dependent on the state of the bits in the IRQ mask

register. The user programs the mask to enable those events,

which are to constitute cause for an IRQ. If an unmasked event

occurs, it triggers the IRQ latch and the IRQ flag is asserted

(active high). The state of the IRQ flag is made available

externally via one of the programmable status pins (see the

Status Pins section).

The automatic assertion of the IRQ flag causes the contents of the

status register to be transferred to the IRQ status register. The

user can then read the IRQ status register any time after the

indication of an IRQ event (that is, assertion of the IRQ flag). By

noting the bit that is set in the IRQ register, the cause of the IRQ

event can be determined.

Once the IRQ register has been read, the user must set the IRQ

reset bit in the appropriate control register via the serial I/O port.

This restores the IRQ flag to its default state, clears the IRQ status

register, and resets the edge detection logic that monitors the

status flags in preparation for the next state change.

06744-

050

20

Q

D

IRQ

REG.

0

IRQ

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

EDGE

DETECT

NEW REF

FREQ. EST. DONE

ENTER HOLDOVER

EXIT HOLDOVER

PHASE LOCKED

PHASE UNLOCKED

FREQ. LOCKED

FREQ. UNLOCKED

REFA LOR

REFB LOR

REFA OOL

REFB OOL

REFA VALID

REFA INVALID

REFB VALID

REFB INVALID

STATUS REGISTER

STATUS

FLAGS

REF SELECTED (A/B)

FREQUENCY EST. DONE

HOLDOVER

PHASE LOCK

FREQUENCY LOCK

REFA LOR

REFB LOR

REFA OOL

REFB OOL

REFA VALID

REFB VALID

RS

T

IRQ RESET

11

IRQ MASK REGISTER

S

Figure 50. Interrupt Request Logic

相关PDF资料 |

PDF描述 |

|---|---|

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

| AD9553BCPZ-REEL7 | IC INTEGER-N CLCK GEN 32LFCSP |

| AD9557BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 40LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

发布紧急采购,3分钟左右您将得到回复。