- 您现在的位置:买卖IC网 > PDF目录1987 > AD9549ABCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9549ABCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 34/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9549A Mask Change 22/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750MHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 4 of 76

SPECIFICATIONS

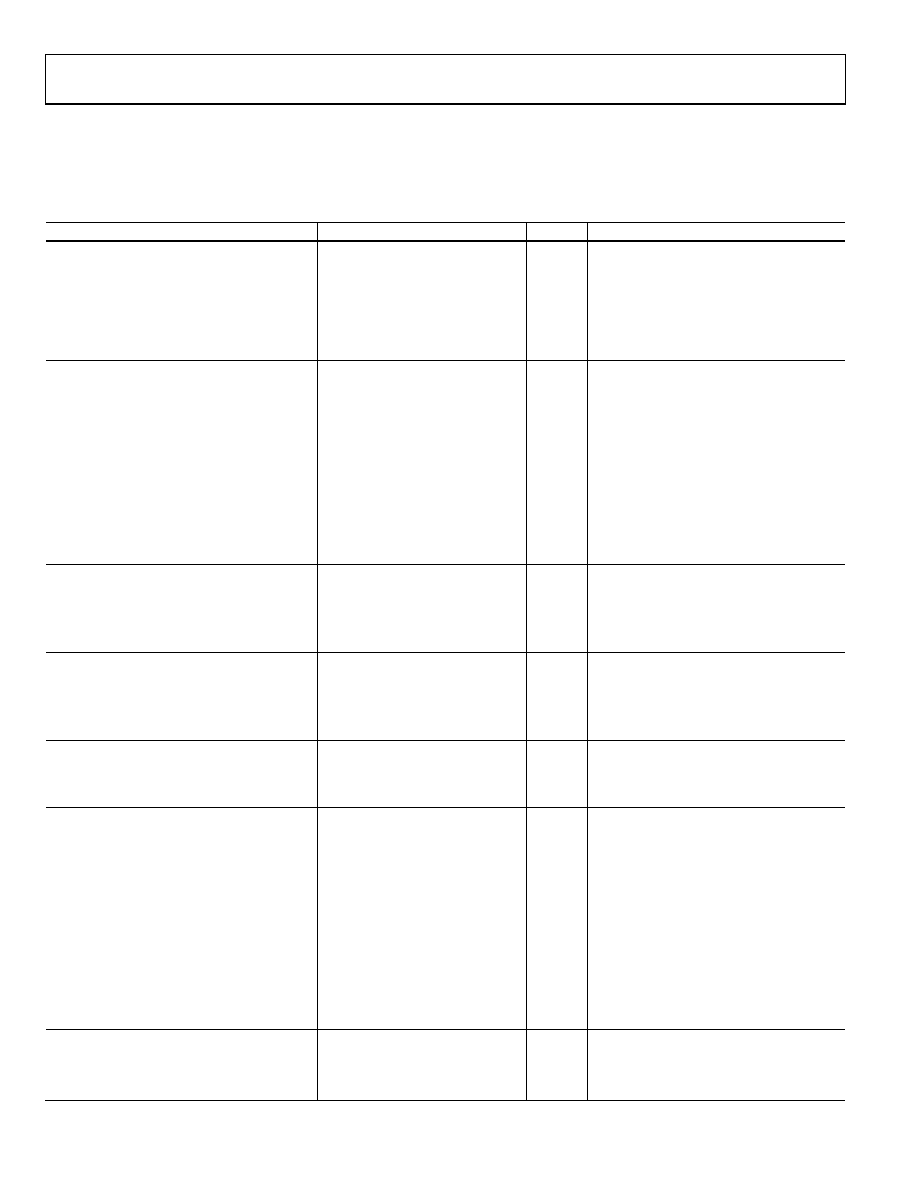

DC SPECIFICATIONS

AVDD = 1.8 V ± 5%, AVDD3 = 3.3 V ± 5%, DVDD = 1.8 V ± 5%, DVDD_I/O = 3.3 V ± 5%. AVSS = 0 V, DVSS = 0 V, unless otherwise noted.

Table 1.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

SUPPLY VOLTAGE

DVDD_I/O (Pin 1)

3.135

3.30

3.465

V

DVDD (Pin 3, Pin 5, Pin 7)

1.71

1.80

1.89

V

AVDD3 (Pin 14, Pin 46, Pin 47, Pin 49)

3.135

3.30

3.465

V

AVDD3 (Pin 37)

1.71

3.30

3.465

V

Pin 37 is typically 3.3 V, but can be set to 1.8 V

AVDD (Pin 11, Pin 19, Pin 23 to Pin 26, Pin 29,

Pin 30, Pin 36, Pin 42, Pin 44, Pin 45, Pin 53)

1.71

1.80

1.89

V

SUPPLY CURRENT

IAVDD3 (Pin 14)

4.7

5.6

mA

REFA, REFB buffers

IAVDD3 (Pin 37)

3.8

4.5

mA

CMOS output clock driver at 3.3 V

IAVDD3 (Pin 46, Pin 47, Pin 49)

26

29

mA

DAC output current source, fS = 1 GSPS

IAVDD (Pin 36, Pin 42)

21

26

mA

FDBK_IN input, HSTL output clock driver

(output doubler turned on)

IAVDD (Pin 11)

12

15

mA

REFA and REFB input buffer 1.8 V supply

IAVDD (Pin 19, Pin 23 to Pin 26, Pin 29,

Pin 30, Pin 44, Pin 45)

215

281

mA

Aggregate analog supply, including system

clock PLL

IAVDD (Pin 53)

41

49

mA

DAC power supply

IDVDD (Pin 3, Pin 5, Pin 7)

254

265

mA

Digital core

IDVDD_I/O (Pin 1)

4

6

mA

Digital I/O (varies dynamically)

LOGIC INPUTS (Except Pin 32)

Pin 9, Pin 10, Pin 54 to Pin 61, Pin 63, Pin 64

Input High Voltage (VIH)

2.0

DVDD_I/O

V

Input Low Voltage (VIL)

DVSS

0.8

V

Input Current (IINH, IINL)

±60

±200

A

At VIN = 0 V and VIN = DVDD_I/O

Maximum Input Capacitance (CIN)

3

pF

CLKMODESEL (Pin 32) LOGIC INPUT

Pin 32 only

Input High Voltage (VIH)

1.4

AVDD

V

Input Low Voltage (VIL)

AVSS

0.4

V

Input Current (IINH, IINL)

18

50

A

At VIN = 0 V and VIN = AVDD

Maximum Input Capacitance (CIN)

3

pF

LOGIC OUTPUTS

Pin 62 and the following bidirectional pins:

Pin 9, Pin 10, Pin 54, Pin 55, Pin 63

Output High Voltage (VOH)

2.7

DVDD_I/O

V

IOH = 1 mA

Output Low Voltage (VOL)

DVSS

0.4

V

IOL = 1 mA

REFERENCE INPUTS

Pin 12, Pin 13, Pin 15, Pin 16

Input Capacitance

3

pF

Input Resistance

8.5

11.5

14.5

k

Differential at Register 0x040F[1:0] = 00

Differential Operation

Common Mode Input Voltage1

1.5

(Applicable When DC-Coupled)

AVDD3

0.2

V

Differential operation; note that LVDS signals

must be ac-coupled

Differential Input Voltage Swing1

500

mV p-p

Differential operation

Single-Ended Operation

Register 0x040F[1:0] = 10

Input Voltage High (VIH)

2.0

AVDD3

V

Input Voltage Low (VIL)

AVSS

0.8

V

Threshold Voltage

AVDD3

0.66

AVDD3

0.82

AVDD3

0.98

V

Register 0x040F[1:0] = 10 (other settings

possible)

Input Current

1

mA

Single-ended operation

FDBK_IN INPUT

Pin 40, Pin 41

Input Capacitance

3

pF

Input Resistance

18

22

26

k

Differential

Differential Input Voltage Swing2

225

mV p-p

12 dBm into 50 ; must be ac-coupled

相关PDF资料 |

PDF描述 |

|---|---|

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

| AD9553BCPZ-REEL7 | IC INTEGER-N CLCK GEN 32LFCSP |

| AD9557BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 40LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

发布紧急采购,3分钟左右您将得到回复。