- 您现在的位置:买卖IC网 > PDF目录1987 > AD9549ABCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9549ABCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9549A Mask Change 22/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750MHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 48 of 76

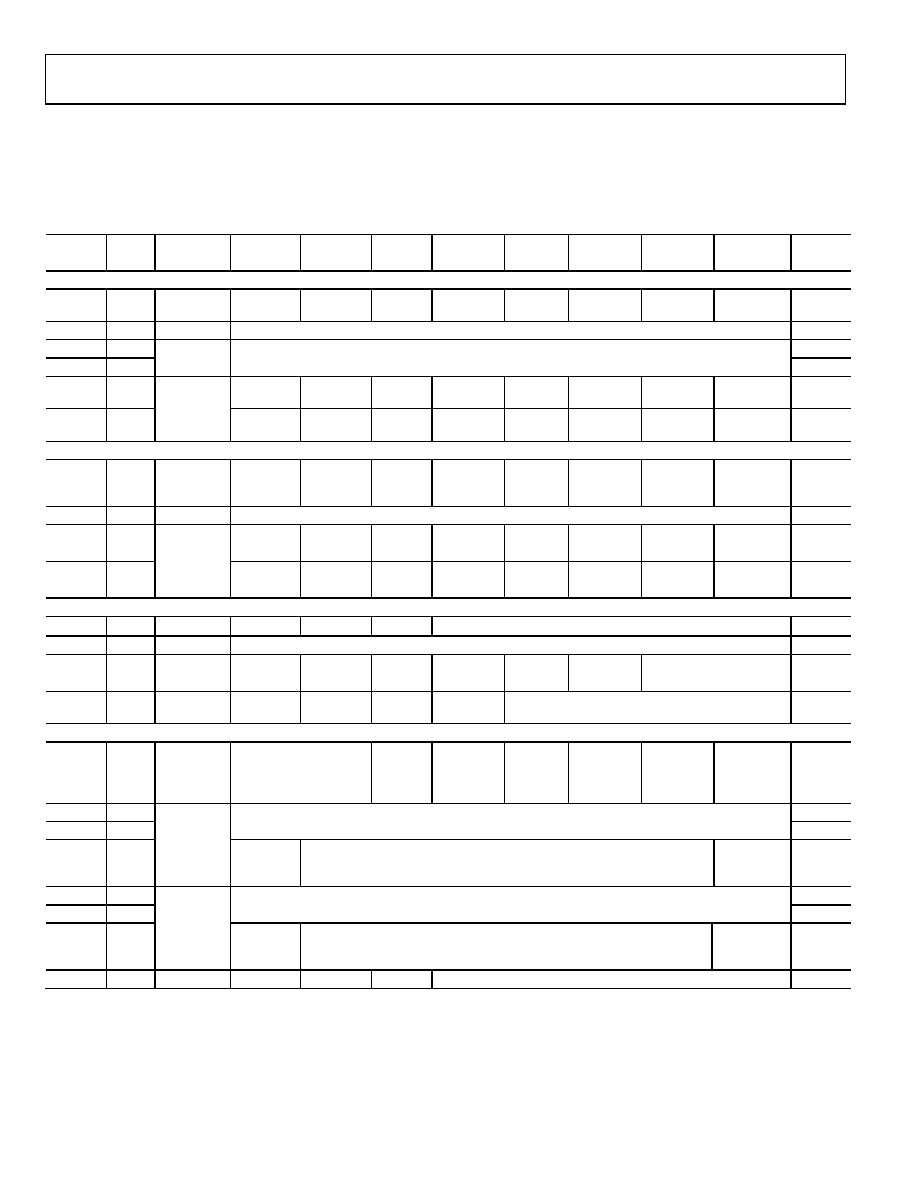

I/O REGISTER MAP

All address and bit locations that are left blank in Table 13 are unused. Accessing reserved registers should be avoided. In cases where

some of the bits in register are reserved, the user can rely on the default value in the I/O register map and write the same value back to the

reserved bits in that register.

Table 13.

Addr

(Hex)

Type1

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

BIt 2

Bit 1

Bit 0

Default

(Hex)

Serial port configuration and part identification

0x0000

Serial

config.

SDO

active

LSB first

(buffered)

Soft

reset

Long

inst.

Long

inst.

Soft reset

LSB first

(buffered)

SDO active

0x18

0x0001

Reserved

0x0002

RO

Part ID

0x82

0x0003

RO

0x09

0x0004

Serial

options

Read buffer

register

0x00

0x0005

AC

Register

update

0x00

Power-down and reset

0x0010

Power-

down and

enable

PD HSTL

driver

Enable

CMOS

driver

Enable

output

doubler

PD

SYSCLK

PLL

PD REFA

PD REFB

Full PD

Digital PD

0x00

0x0011

Reserved

0x0012

M, AC

Reset

History

reset

IRQ

reset

FPFD

reset

CPFD

reset

LF reset

CCI reset

DDS reset

0x00

0x0013

M

PD fund

DDS

S-div/2

reset

R-div/2

reset

S-divider

reset

R-divider

reset

0x00

System clock

0x0020

N-divider

N-divider, Bits[4:0]

0x12

0x0021

Reserved

0x0022

PLL

parameters

VCO auto

range

2×

reference

VCO range

Charge pump current,

Bits[1:0]

0x04

0x0023

PFD

divider

PFD divider, Bits[3:0]

(relationship between SYSCLK and PFD clock)

0x05

DPLL

0x0100

M

PLL

control

Reserved

Single-

tone

mode

Disable

freq.

estimator

Enable

freq.

slew

limiter

Reserved

Loop

polarity

Close loop

0x30

0x0101

R-divider

R-divider, Bits[15:0]

0x00

0x0102

0x00

0x0103

Falling

edge

triggered

Reserved

R-divider/2

0x00

0x0104

S-divider

S-divider, Bits[15:0]

0x00

0x0105

0x00

0x0106

Falling

edge

triggered

Reserved

S-divider/2

0x00

0x0107

M

P-divider

P-divider, Bits[4:0]

0x05

相关PDF资料 |

PDF描述 |

|---|---|

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

| AD9553BCPZ-REEL7 | IC INTEGER-N CLCK GEN 32LFCSP |

| AD9557BCPZ-REEL7 | IC CLK XLATR PLL 1250MHZ 40LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

发布紧急采购,3分钟左右您将得到回复。