参数资料

| 型号: | DS3105LN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 102/124页 |

| 文件大小: | 0K |

| 描述: | IC TIMING LINE CARD 64-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 类型: | 定时卡 IC,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum,电信 |

| 输入: | CMOS,LVDS,LVPECL,TTL |

| 输出: | CMOS,LVDS,LVPECL,TTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 5:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 312.5MHz |

| 电源电压: | 1.62 V ~ 1.98 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页当前第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页

DS3105

79

Register Name:

MCR10

Register Description:

Master Configuration Register 10

Register Address:

48h

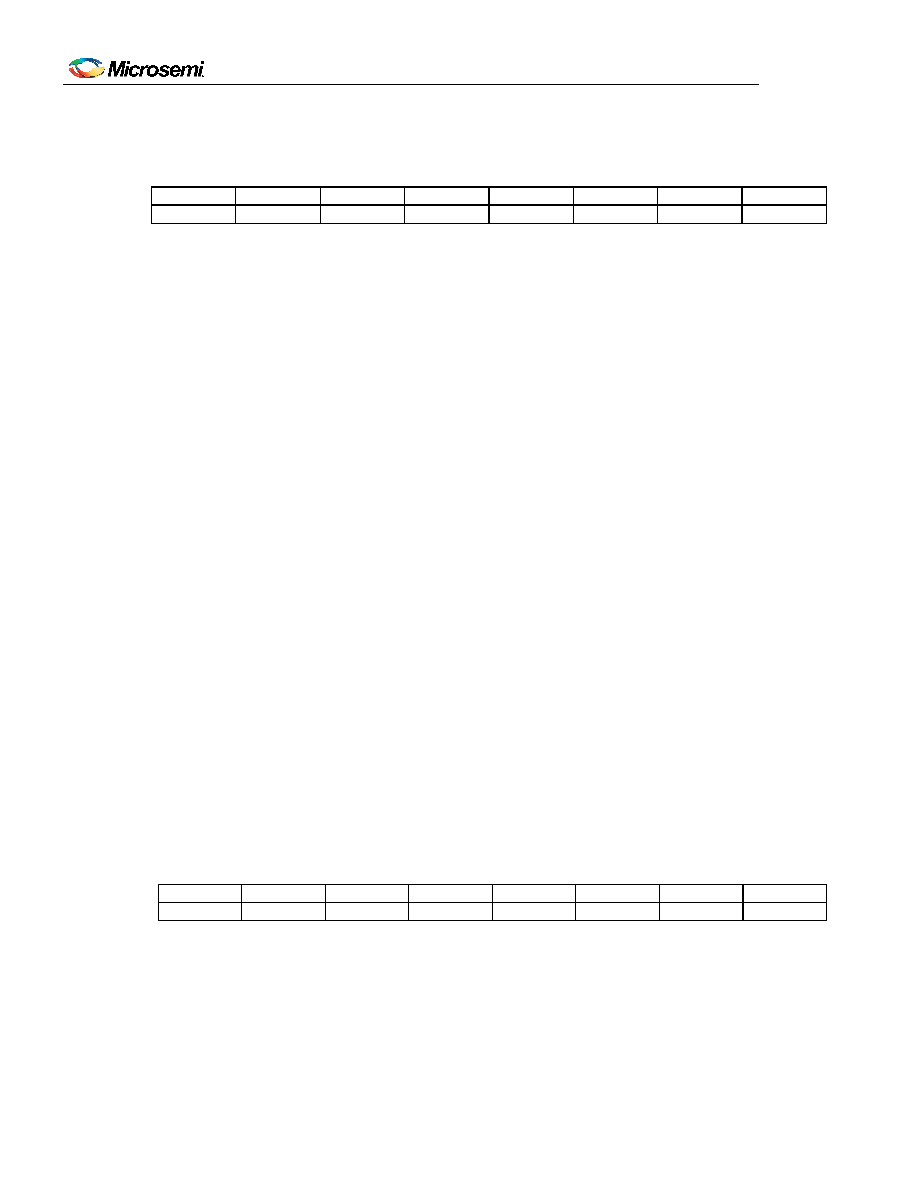

Bit #

7

6

5

4

3

2

1

0

Name

—

SRFPIN

UFSW

EXTSW

PBOFRZ

PBOEN

—

Default

1

0

see below

0

1

0

Bit 6: SRFAIL Pin Enable (SRFPIN). When this bit is set to 1, the SRFAIL pin is enabled. When enabled the

SRFAIL pin follows the state of the SRFAIL status bit in the MSR2 register. This gives the system a very fast

indication of the failure of the current reference. See Section 7.5.3.

0 = SRFAIL pin disabled (high impedance)

1 = SRFAIL pin enabled

Bit 5: Ultra-Fast Switching Mode (UFSW). See Section 7.6.4.

0 = Disabled

1 = Enabled. The current reference source is disqualified after less than three missing clock cycles.

Bit 4: External Reference Switching Mode (EXTSW). This bit enables external reference switching mode. In this

mode, if the SRCSW pin is high the T0 DPLL is forced to lock to input IC3 (if the priority of IC3 is nonzero) or IC5 (if

the priority of IC3 is zero) whether or not the selected input has a valid reference signal. If the SRCSW pin is low

the device is forced to lock to input IC4 (if the priority of IC4 is nonzero) or IC6 (if the priority of IC4 is zero) whether

or not the selected input has a valid reference signal. During reset the default value of this bit is latched from the

SRCSW pin. This mode only controls the T0 DPLL. The T4 DPLL is not affected. See Section 7.6.5.

0 = Normal operation

1 = External switching mode

Bit 3: Phase Build-Out Freeze (PBOFRZ). This bit freezes the current input-output phase relationship and does

not allow further phase build-out events to occur. This bit affects phase build-out in response to reference switching

(Section 7.7.7.1).

0 = Not frozen

1 = Frozen

Bit 2: Phase Build-Out Enable (PBOEN). When this bit is set to 1 a phase build-out event occurs every time the

T0 DPLL changes to a new reference, including exiting the holdover and free-run states. When this bit is set to 0,

the T0 DPLL locks to the new source with zero degrees of phase difference. See Section 7.7.7.

Register Name:

MCR11

Register Description:

Master Configuration Register 11

Register Address:

4Bh

Bit #

7

6

5

4

3

2

1

0

Name

—

T4T0

—

Default

0

Bit 4: T4 or T0 Path Select (T4T0). This bit specifies which path is being accessed when reads or writes are made

to the following registers: PTAB1, PTAB2, FREQ1, FREQ2, FREQ3, IPR2, IPR3, IPR5, PHASE1, and PHASE2.

0 = T0 path

1 = T4 path

相关PDF资料 |

PDF描述 |

|---|---|

| DS3106LN+ | IC TIMING LINE CARD 64-LQFP |

| DS3231MZ+ | IC RTC I2C 8SOIC |

| DS3231SN#T&R | IC RTC W/TCXO 16-SOIC |

| DS3232MZ+ | IC RTC W/SRAM I2C 8SOIC |

| DS3232SN#T&R | IC RTC W/TCXO 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3105LN+ | 功能描述:计时器和支持产品 Line Card Timing IC RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| DS3106 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Line Card Timing IC |

| DS3106A10SL3S(621) | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S(621) | 制造商:Amphenol Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。