参数资料

| 型号: | DS3105LN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 7/124页 |

| 文件大小: | 0K |

| 描述: | IC TIMING LINE CARD 64-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 类型: | 定时卡 IC,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum,电信 |

| 输入: | CMOS,LVDS,LVPECL,TTL |

| 输出: | CMOS,LVDS,LVPECL,TTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 5:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 312.5MHz |

| 电源电压: | 1.62 V ~ 1.98 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页

DS3105

104

9.

JTAG Test Access Port and Boundary Scan

9.1

JTAG Description

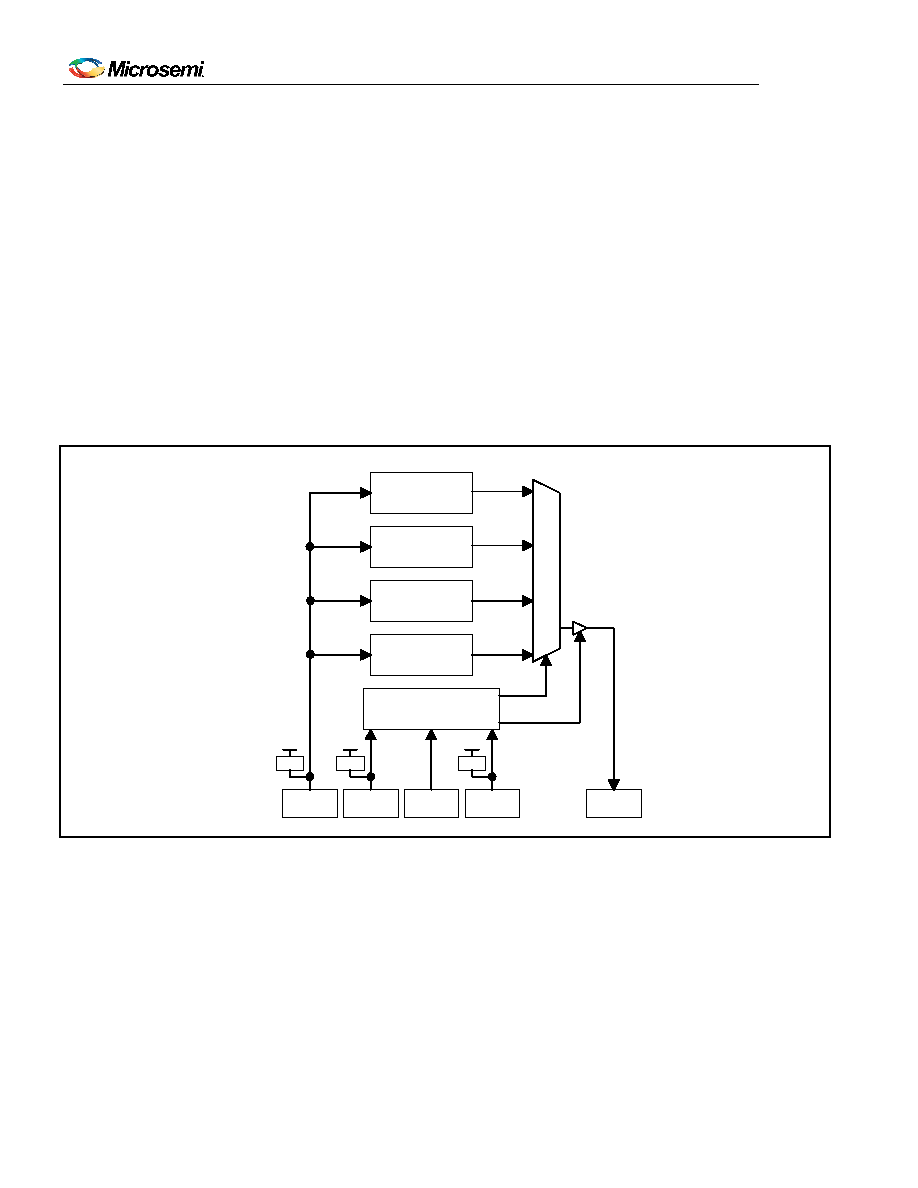

The DS3105 supports the standard instruction codes SAMPLE/PRELOAD, BYPASS, and EXTEST. Optional public

instructions included are HIGHZ, CLAMP, and IDCODE. Figure 9-1 shows a block diagram. The DS3105 contains

the following items, which meet the requirements set by the IEEE 1149.1 Standard Test Access Port and Boundary

Scan Architecture:

Test Access Port (TAP)

Bypass Register

TAP Controller

Boundary Scan Register

Instruction Register

Device Identification Register

The TAP has the necessary interface pins, namely JTCLK,

JTRST, JTDI, JTDO, and JTMS. Details on these pins

can be found in Table 6-5. Details about the boundary scan architecture and the TAP can be found in IEEE 1149.1-

1990, IEEE 1149.1a-1993, and IEEE 1149.1b-1994.

Figure 9-1. JTAG Block Diagram

BOUNDARY SCAN

REGISTER

DEVICE

IDENTIFICATION

REGISTER

BYPASS REGISTER

INSTRUCTION

REGISTER

TEST ACCESS PORT

CONTROLLER

MUX

SELECT

THREE-STATE

JTDI

50k

JTMS

50k

JTCLK

JTRST

50k

JTDO

相关PDF资料 |

PDF描述 |

|---|---|

| DS3106LN+ | IC TIMING LINE CARD 64-LQFP |

| DS3231MZ+ | IC RTC I2C 8SOIC |

| DS3231SN#T&R | IC RTC W/TCXO 16-SOIC |

| DS3232MZ+ | IC RTC W/SRAM I2C 8SOIC |

| DS3232SN#T&R | IC RTC W/TCXO 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3105LN+ | 功能描述:计时器和支持产品 Line Card Timing IC RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| DS3106 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Line Card Timing IC |

| DS3106A10SL3S(621) | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S(621) | 制造商:Amphenol Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。