参数资料

| 型号: | DS3105LN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 124/124页 |

| 文件大小: | 0K |

| 描述: | IC TIMING LINE CARD 64-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 类型: | 定时卡 IC,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum,电信 |

| 输入: | CMOS,LVDS,LVPECL,TTL |

| 输出: | CMOS,LVDS,LVPECL,TTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 5:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 312.5MHz |

| 电源电压: | 1.62 V ~ 1.98 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页当前第124页

DS3105

99

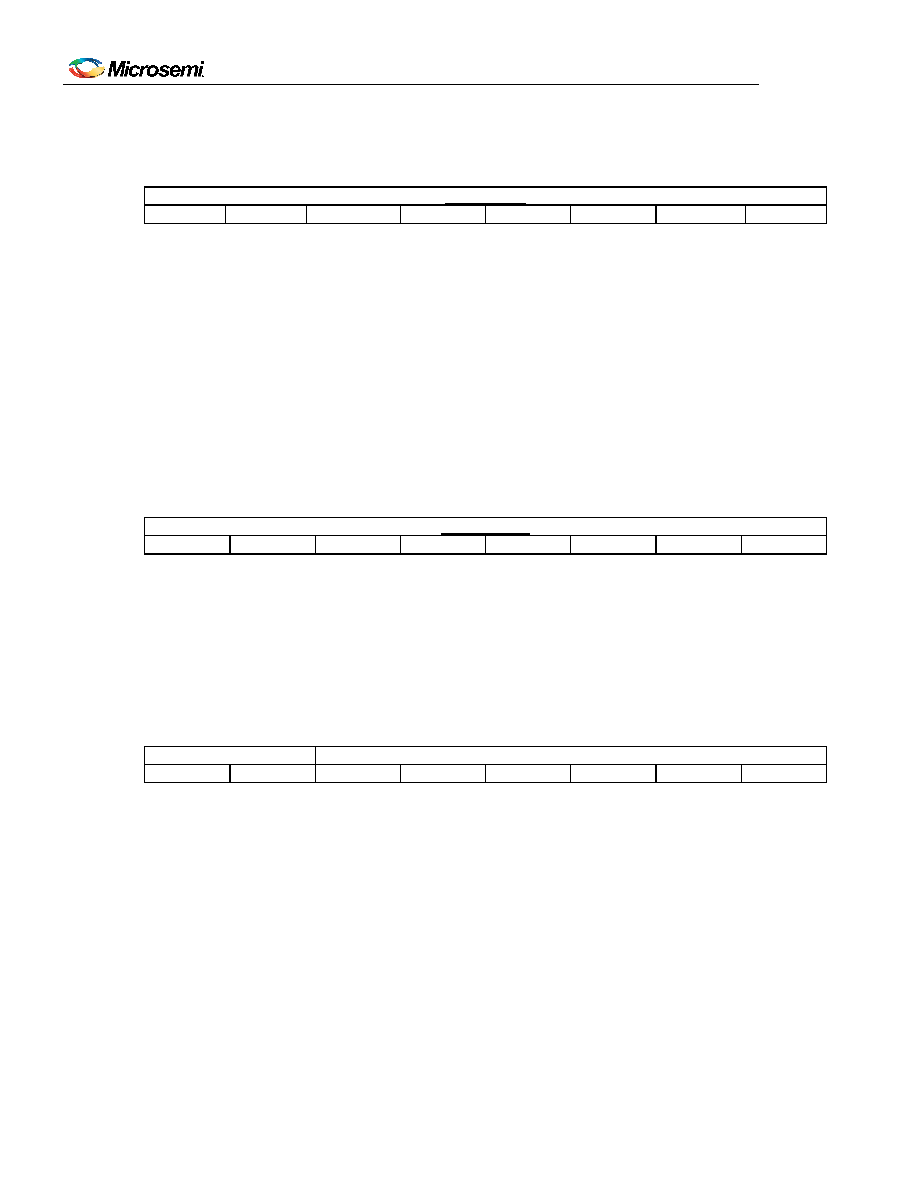

Register Name:

PHASE1

Register Description:

Phase Register 1

Register Address:

77h

Bit #

7

6

5

4

3

2

1

0

Name

PHASE[7:0]

Default

0

Note: The PHASE1 and PHASE2 registers must be read consecutively. See Section 8.3.

Bits 7 to 0: Current DPLL Phase (PHASE[7:0]). The full 16-bit PHASE[15:0] field spans this register and the

PHASE2 register. PHASE is a two’s-complement signed integer that indicates the current value of the phase

detector. The value is the output of the phase averager. When T4T0 = 0 in the MCR11 register, PHASE indicates

the current phase of the T0 DPLL. When T4T0 = 1, PHASE indicates the current phase of the T4 DPLL. The

averaged phase difference in degrees is equal to PHASE

× 0.707. See Section 7.7.10.

Register Name:

PHASE2

Register Description:

Phase Register 2

Register Address:

78h

Bit #

7

6

5

4

3

2

1

0

Name

PHASE[15:8]

Default

0

Bits 7 to 0: Current DPLL Phase (PHASE[15:8]). See the PHASE1 register description.

Register Name:

PHLKTO

Register Description:

Phase-Lock Timeout Register

Register Address:

79h

Bit #

7

6

5

4

3

2

1

0

Name

PHLKTOM[1:0]

PHLKTO[5:0]

Default

0

1

0

1

0

Bits 7 and 6: Phase-Lock Timeout Multiplier (PHLKTOM[1:0]). This field is an unsigned integer that specifies

the resolution of the phase-lock timeout field PHLKTO[5:0].

00 = 2 seconds

01 = 4 seconds

10 = 8 seconds

11 = 16 seconds

Bits 5 to 0: Phase-Lock Timeout (PHLKTO[5:0]). This field is an unsigned integer that, together with the

PHLKTOM[1:0] field, specifies the length of time that the T0 DPLL attempts to lock to an input clock before

declaring a phase-lock alarm (by setting the corresponding LOCK bit in the ISR registers). The timeout period in

seconds is PHLKTO[5:0]

× 2^(PHLKTOM[1:0] + 1). The state machine remains in the prelocked, prelocked 2, or

phase-lost modes for the specified time before declaring a phase alarm on the selected input. See Section 7.7.1.

相关PDF资料 |

PDF描述 |

|---|---|

| DS3106LN+ | IC TIMING LINE CARD 64-LQFP |

| DS3231MZ+ | IC RTC I2C 8SOIC |

| DS3231SN#T&R | IC RTC W/TCXO 16-SOIC |

| DS3232MZ+ | IC RTC W/SRAM I2C 8SOIC |

| DS3232SN#T&R | IC RTC W/TCXO 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3105LN+ | 功能描述:计时器和支持产品 Line Card Timing IC RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| DS3106 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Line Card Timing IC |

| DS3106A10SL3S(621) | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S | 制造商:Amphenol Corporation 功能描述: |

| DS3106A14S2S(621) | 制造商:Amphenol Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。