- 您现在的位置:买卖IC网 > Datasheet目录327 > HW-V5-ML561-UNI-G (Xilinx Inc)EVALUATION PLATFORM VIRTEX-5 Datasheet资料下载

参数资料

| 型号: | HW-V5-ML561-UNI-G |

| 厂商: | Xilinx Inc |

| 文件页数: | 138/140页 |

| 文件大小: | 0K |

| 描述: | EVALUATION PLATFORM VIRTEX-5 |

| 产品变化通告: | Adapter Replacement 23/May/2008 Development Systems Discontinuation 16/Jan/2012 |

| 标准包装: | 1 |

| 系列: | Virtex®-5 LXT |

| 类型: | FPGA |

| 适用于相关产品: | XC5VLX50T-FFG1136 |

| 所含物品: | 开发平台,小型闪存卡,缆线,DDR2 DIMM,电源和软件 |

| 相关产品: | XC5VLX50T-3FFG665C-ND - IC FPGA VIRTEX-5 50K 665FCBGA XC5VLX50T-3FFG1136C-ND - IC FPGA VIRTEX-5 50K 1136FBGA XC5VLX50T-3FF665C-ND - IC FPGA VIRTEX-5 50K 665FCBGA XC5VLX50T-3FF1136C-ND - IC FPGA VIRTEX-5 50K 1136FBGA XC5VLX50T-2FFG665I-ND - IC FPGA VIRTEX-5 50K 665FCBGA XC5VLX50T-2FFG665C-ND - IC FPGA VIRTEX-5 50K 665FCBGA XC5VLX50T-2FFG1136I-ND - IC FPGA VIRTEX-5 50K 1136FBGA XC5VLX50T-2FFG1136C-ND - IC FPGA VIRTEX-5 50K 1136FBGA XC5VLX50T-2FF665I-ND - IC FPGA VIRTEX-5 50K 665FCBGA XC5VLX50T-2FF665C-ND - IC FPGA VIRTEX-5 50K 665FCBGA 更多... |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页当前第138页第139页第140页

�� �

�

�

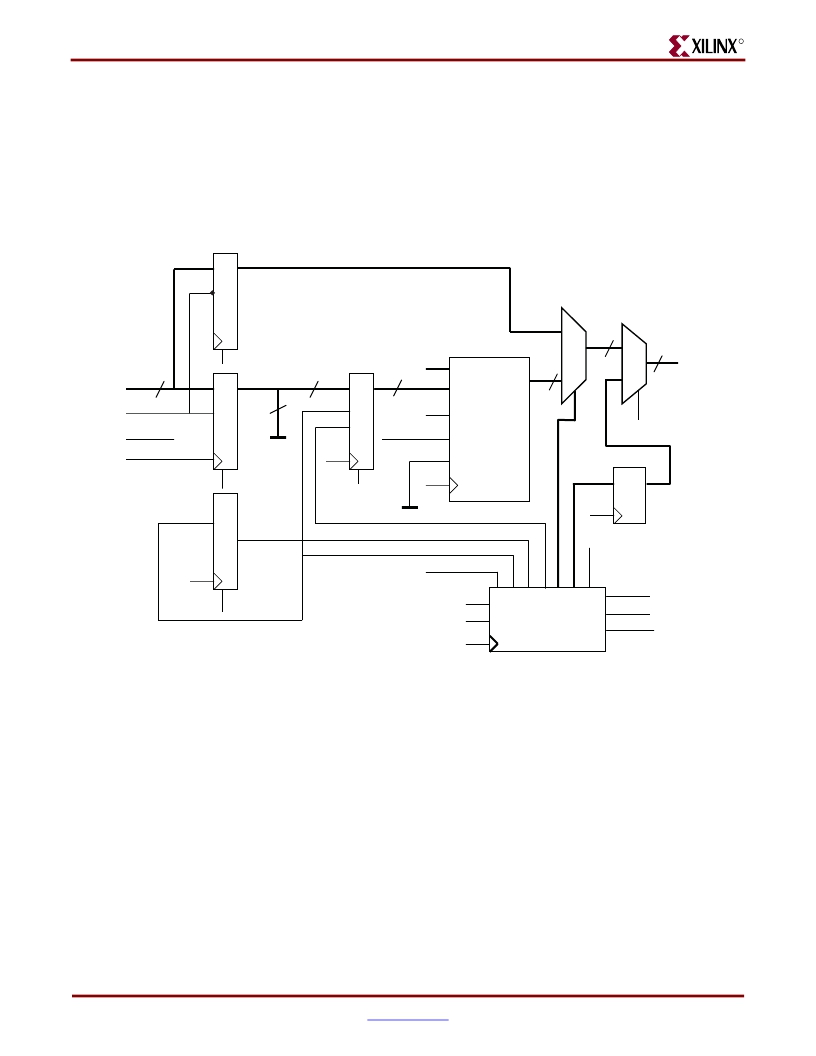

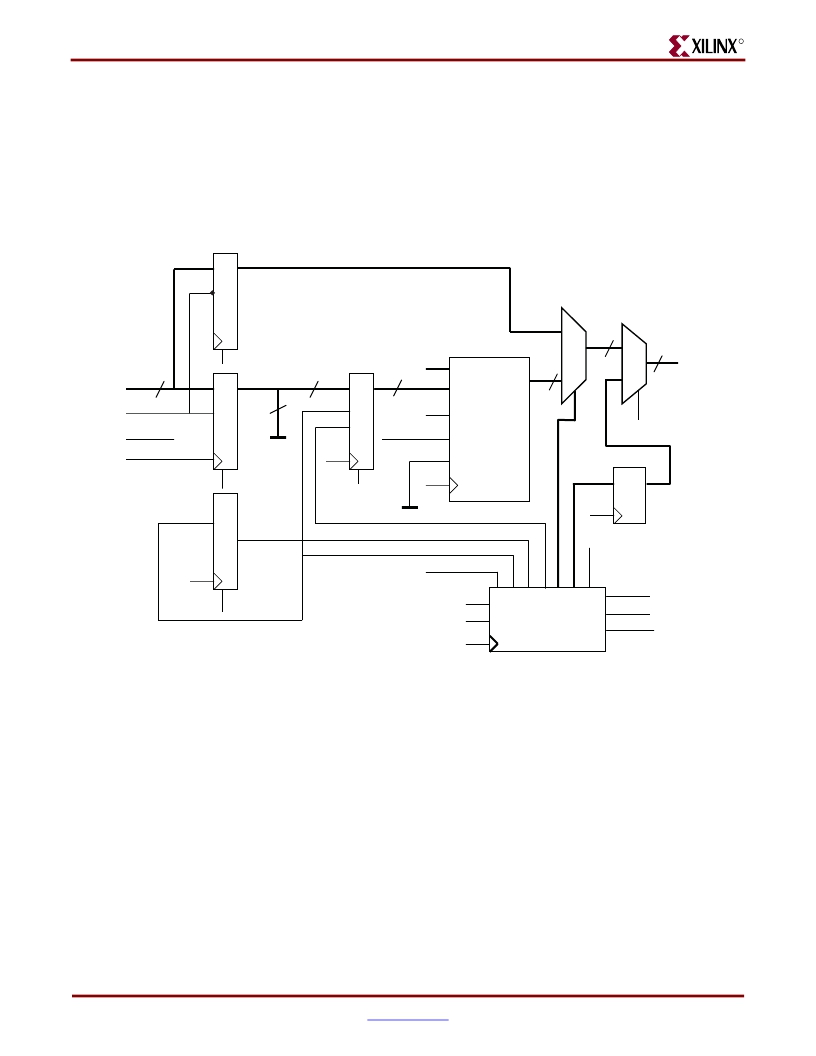

�Appendix� C:� LCD� Interface�

�R�

��data� is� latched� and� then� shifted� left� three� positions.� This� shifted� value� is� the� start� byte� for� a�

�counter� that� outputs� an� address� to� the� block� RAM.� The� result� is� a� stream� of� bytes�

�representing� a� character� for� the� display.�

�A� small� second� counter� determines� when� a� new� character� is� loaded� into� the� block� RAM�

�address� counter.�

�Po� s� ition�

�Regi� s� ter�

�P� a� ge�

�8�

�D� a� t� a� In�

�De� s� R� s� t�

�11�

�Co� u� nter� A�

�11�

�DI�

�Addr�

�DO�

�8�

�0�

�1�

�8�

�D� a� t� a�

�En� a�

�R� s� t�

�Clk�

�8�

�E�

�Di� s� pl� a� y�

�3�

�Clk�

�E�

�L�

�De� s� R� s� t�

�En� a�

�Ss� r�

�We�

�RAMB16_� S� 9�

�Regi� s� ter�

�De� s� R� s� t�

�De� s� R� s� t�

�Clk�

�Clk�

�Co� u� nter� B�

�E�

�TC�

�Lo� a� d�

�LUT-ROM�

�Di� s� pl� a� y�

�Clk�

�Co� u� nt� to� 8.�

�De� s� R� s� t�

�Initi� a� liz� a� tion�

�De� s� R� s� t�

�S� top� b� oth� co� u� nter� s� a� t� TC.�

�S� end� ch� a� r� a� cter� po� s� ition� a� nd�

�line� to� the� LCD.�

�Lo� a� d� new� v� a� l� u� e� in� co� u� nter� A.�

�R� s� t�

�En� a�

�S� t� a� te� M� a� chine�

�R� S�

�RW�

�E�

�S� witch� to� ch� a� r� a� cter� ROM.�

�Clk�

�En� ab� le� co� u� nter� s� .�

�UG199_C_11_050106�

�Figure� C-11:�

�LCD� Character� Generator� Controller�

�A� state� machine� manages� the� processing� order.�

�A� minimum� cycle� time� of� 400� ns� on� the� E� signal� used� as� a� reference.� The� 200� MHz� system�

�clock� frequency� is� used� as� reference� system� clock.� One� E� cycle� uses� at� least� 80� system� clock�

�cycles� when� the� design� is� running� at� 200� MHz.� The� E� pulse� is� part� of� the� state� machine,� and�

�the� design� only� depends� on� the� system� clock.� Timing� is� met� as� long� as� the� system� clock�

�does� not� exceed� 200� MHz.�

�This� design� can� be� adapted� easily� to� fit� the� MicroBlaze?� or� PPC405� CoreConnect� bus�

�system.�

�138�

��Virtex-5� FPGA� ML561� User� Guide�

�UG199� (v1.2.1)� June� 15,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| I-JET | JTAG ARM DEBUGGING PROBE |

| IAC24A | INPUT MODULE AC 5MA 24VDC |

| IAC5EQ | INPUT MODULE AC 10MA 5VDC |

| IB8RM | SURGE SUPP 8OUT 12'CORD W/REMOTE |

| IBAR12-20T | SURGE SUPPRSSR 20A 12OUT RACKMNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HW-V5-ML561-UNI-G-J | 功能描述:EVALUATION PLATFORM VIRTEX-5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-5 LXT 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| HW-V5-PCIE2-UNI-G | 功能描述:KIT DEV PCIEXPRESS GTX VIRTEX5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex® -5 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| HW-VID-KIT | 功能描述:可编程逻辑 IC 开发工具 Lattice Video Interface Kit RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| HW-VL1 | 制造商:IDEC CORPORATION 功能描述:BARRIER |

| HW-VL2 | 制造商:IDEC Corporation 功能描述:COVER;HW FNGR SAFE CONTAC CVR 制造商:IDEC CORPORATION 功能描述:HW FNGR SAFE CONTAC CVR |

发布紧急采购,3分钟左右您将得到回复。