参数资料

| 型号: | HW-XGI-VIDEO-US |

| 厂商: | Xilinx Inc |

| 文件页数: | 38/68页 |

| 文件大小: | 0K |

| 描述: | DAUGHTER CARD VIDEO I/O VIODC |

| 标准包装: | 1 |

| 其它名称: | 122-1506 HW-XGI-VIDEO-US-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

�� �

�

�

�Chapter� 4:� DVI/VGA� Input� Interface�

�R�

�The� VSOUT� output� is� an� unmodified� signal� from� the� selected� source.� In� analog� mode� with�

�separate� syncs,� it� is� simply� a� passthrough� from� the� VSYNC� input.� If� the� analog� input� is�

�using� a� composite� sync� mode,� VSOUT� is� the� recovered� vertical� sync.� In� DVI� mode,� VSOUT�

�is� the� decoded� VSYNC� from� the� serial� digital� stream.�

�In� analog� modes,� the� HSOUT� is� a� reconstructed� version� of� the� HSYNC� input� or� horizontal�

�sync� from� the� composite� sync.� Registers� allow� adjustment� of� the� polarity� and� duration� of�

�this� signal.� In� DVI� mode,� HSOUT� is� the� decoded� HSYNC� from� the� serial� digital� stream.�

�DE� is� only� available� in� DVI� mode.� This� signal� qualifies� the� pixel� data� as� active� pixels.� In�

�analog� mode,� this� signal� is� high,� and� the� pixels� must� be� qualified� elsewhere.�

�DVI� Input�

�The� Digital� Visual� Interface� (DVI)� is� a� digital� replacement� for� analog� VGA.� It� is� simply� a�

�digital� version� of� the� above� described� analog� interface,� with� the� same� scan� order� and�

�timing.� Instead� of� analog� voltages� for� the� video� data,� the� data� is� serially� encoded� digital�

�values.� This� method� for� high-speed� serial� data� is� called� transition� minimized� differential�

�signaling� (TMDS).� TMDS� is� a� combination� of� the� electrical� signal� specification� and� the�

�encoding� scheme.� The� electrical� signal� specifications� are� similar� to� LVDS.� The� encoding�

�scheme� results� in� 10-bit� symbols� for� each� 8-bit� byte,� thus� the� encoded� bit� rate� is� 10x� the� byte�

�rate.� Each� pixel� is� encoded� as� a� 24-bit� value,� 8-bits� for� each� color.� Just� like� VGA,� each� color�

�is� transferred� separately,� so� each� color� has� its� own� differential� pair.� This� means� that� the�

�encoded� bit� rate� is� 10x� the� pixel� rate.� DVI� also� requires� a� separate� clock� reference� signal,�

�increasing� the� number� of� differential� pairs� to� 4.� The� 10-bit� encoding� also� includes� some�

�special� symbols,� allowing� the� sync� signals� to� be� included� with� the� green� signal� (a� digital�

�SOG).�

�Other� than� the� digital� encoding,� there� is� one� significant� difference� in� interfacing� to� DVI.�

�The� TMDS� encoding� also� allows� a� data� enable� (DE)� signal� to� be� carried� with� the� data.� This�

�signal� is� very� useful� to� digital� systems,� as� it� easily� qualifies� the� data.� In� the� analog� VGA�

�scheme,� the� only� way� to� know� when� the� data� is� valid� is� to� know� specific� timing�

�relationships� with� respect� to� the� sync� signals.�

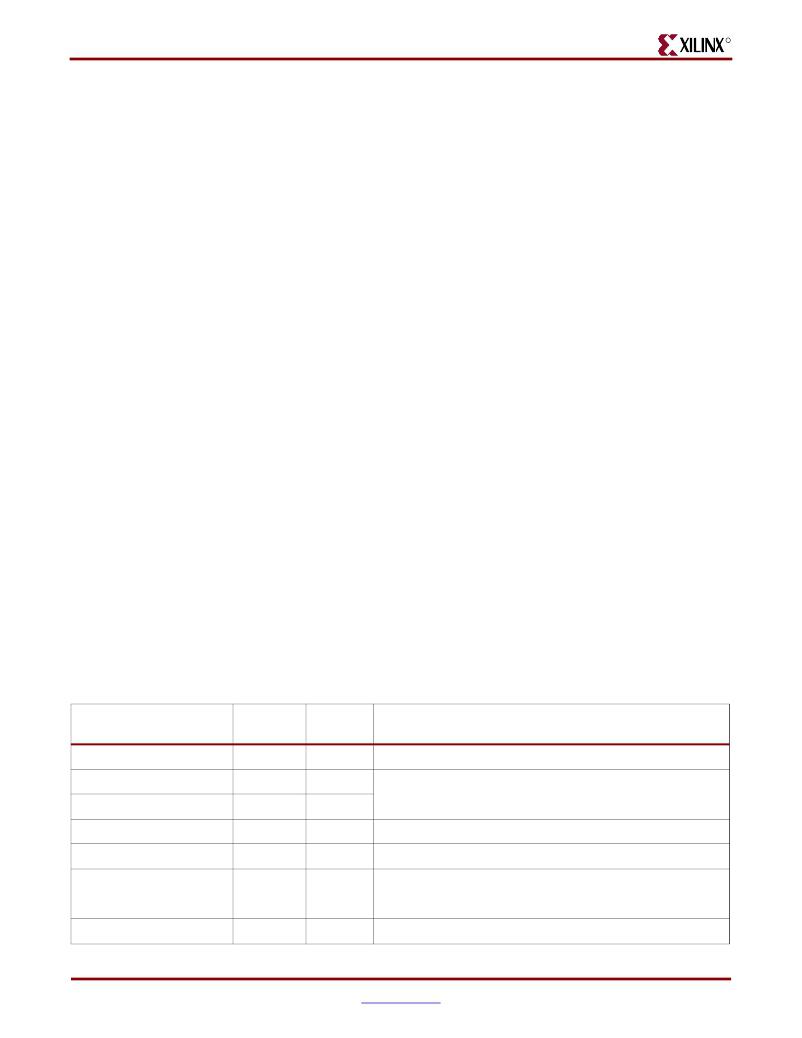

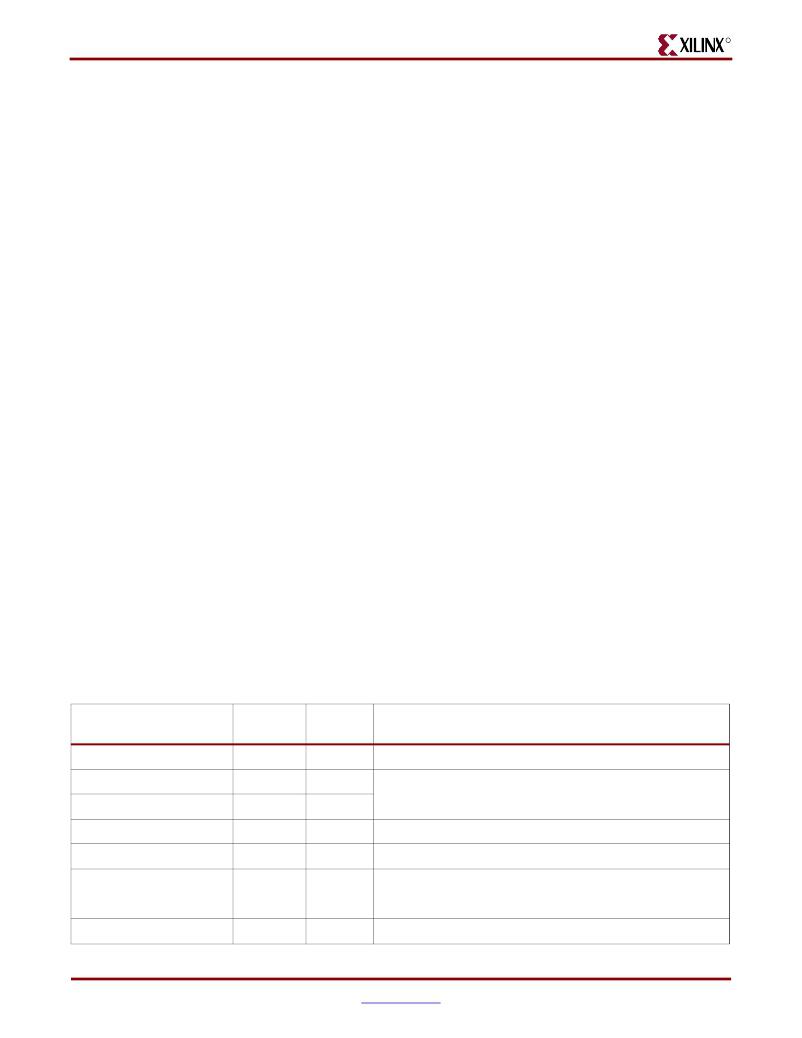

�I2C� Initialization� Table� (in� Hex)�

�All� I2C� communications� to� the� AD9887A� is� at� address� 0x9a/9B.� See� Table� 4-2� through�

��Table� 4-2:� Analog� VGA60�

�Register� Name�

�Active� Interface�

�PLL� Div� MSB�

�PLL� Div� LSB�

�VCO/CPMP�

�Phase� Adjust�

�Clamp� Placement�

�Clamp� Duration�

�HSOUT� Pulse� width�

�Register�

�Address�

�0x12�

�0x01�

�0x02�

�0x03�

�0x04�

�0x05�

�0x06�

�0x07�

�Register�

�Value�

�0x81�

�0x41�

�0xF0�

�0x8C�

�0x80�

�0x24�

�0x24�

�0x80�

�Description�

�Force� selection� of� analog� input�

�PLL� divider� value.� VGA60� has� 1056� cycles� per� HSYNC�

�period.� 1056� -1� =� 0x41F�

�VCORNGE� =� 00,� CURRENT� =� 011�

�Default� phase� =� T/2�

�36� cycles� after� HSYNC�

�36� cycles� in� duration�

�128� cycles� in� HSYNC�

�38�

��Video� Input/Output� Daughter� Card�

�UG235� (v1.2.1)� October� 31,� 2007�

�相关PDF资料 |

PDF描述 |

|---|---|

| ICD15S13E6GV00LF | CONN DSUB HD SOCKT 15POS R/A PCB |

| ICD26S13E4GX00LF | CONN DSUB HD SOCKT 26POS R/A PCB |

| ID09S33E4GV00LF | CONN RCPT 9POS R/A GOLD |

| ID451000 | CONN RECPT USB A ADAPTER |

| IELHK11-1-72-70.0-01-V | CIRCUIT BREAKER HYMAG DP 70A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HWXX35338TR | 制造商:Vishay Intertechnologies 功能描述: |

| HWXX38438 | 制造商:Vishay Semiconductors 功能描述: |

| HWZ1408 | 制造商:OHIO BUCKEYE 功能描述: |

| HWZ1424 | 制造商:OHIO BUCKEYE 功能描述: |

| HWZ1620 | 制造商:OHIO BUCKEYE 功能描述: |

发布紧急采购,3分钟左右您将得到回复。